# Front-End ASIC for a Liquid Argon TPC

Gianluigi De Geronimo, Alessio D'Andragora, Shaorui Li, Neena Nambiar, Sergio Rescia, Emerson Vernon, Hucheng Chen, Francesco Lanni, Don Makowiecki, Veljko Radeka, Craig Thorn, and Bo Yu

Abstract—We present a front-end application-specific integrated circuit (ASIC) for a wire based time-projection-chamber (TPC) operating in liquid Argon (LAr). The LAr TPC will be used for long baseline neutrino oscillation experiments. The ASIC must provide a low-noise readout of the signals induced on the TPC wires, digitization of those signals at 2 MSamples/s, compression, buffering and multiplexing. A resolution of better than 1000 rms electrons at 200 pF input capacitance for an input range of 300 fC is required, along with low power and operation in LAr (at 87 K). We include the characterization of a commercial technology for operation in the cryogenic environment and the first experimental results on the analog front end. The results demonstrate that complementary metal-oxide semiconductor transistors have lower noise and much improved dc characteristics at LAr temperature. Finally, we introduce the concept of "1/f equivalent" to model the low-frequency component of the noise spectral density, for use in the input metal-oxide semiconductor field-effect transistor optimization.

Index Terms— Analog-to-digital converter (ADC), applicationspecific integrated circuit (ASIC), cryogenic, noise.

#### I. INTRODUCTION

■ HE LONG Baseline Neutrino Experiment (LBNE) [1], [2] aims at employing the high-power neutrino beams produced by the main injector accelerator at Fermi National Laboratory to explore neutrino oscillations, interactions, and transformations. The experimental hall will be located about 1000 km away at the site of the Homestake Mine, SD. The proposed detector will be composed of one or more 20 kton cryostats, each with size  $70 \times 15 \times 15$  m<sup>3</sup>. The modular electrode design of the wire-based Liquid Argon (LAr) time projection chamber (TPC) is described in [3]. In each wire frame module, the wires are grouped in three coplanar layers [4]. An electric field is applied in the ( $\sim$ 2.5 m) drift space between the cathode and the readout planes, and the electrons generated by the ionizing tracks drift toward the readout wires. The first two wire planes are biased so that the electrons pass between the wires and are collected on the third plane. The first two wire planes, oriented at some angle with respect to the collecting wires, observe induced bipolar current signals and no net charge. The total number of wires in each module is on the order of 600 000, and the length

Manuscript received November 20, 2010; revised January 24, 2011; accepted March 05, 2011. Date of publication April 21, 2011; date of current version June 15, 2011.

G. De Geronimo, S. Li, N. Nambiar, S. Rescia, E. Vernon, H. Chen, F. Lanni, D. Makowiecki, V. Radeka, C. Thorn, and B. Yu are with the Brookhaven National Laboratory, Upton, NY 11973-5000 USA (e-mail: degeronimo@bnl.gov).

A. D'Andragora is with the University of L'Aquila, L'Aquila 67100, Italy. Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TNS.2011.2127487

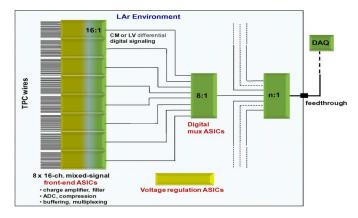

Fig. 1. Block diagram illustrating the architecture of the readout electronics for the LAr TPC. The ASICs must operate at LAr temperature (87 K), in close proximity to the ends of the detecting wires.

and capacitance of each wire can approach, respectively, 10 m and 200 pF. For each wire, the front-end channel must read out charge signals up to 300 fC with a resolution of better than 1000 rms electrons, must digitize with 12-bit resolution at a rate of 2 MSamples/s (MS/s), and must compress, buffer, and multiplex the data to reduce the number of module feedthrough pins to a few thousands. The power dissipated by each channel must be constrained within  $\sim \! 10$  mW.

Fig. 1 shows the architecture of the LAr TPC readout electronics, submerged in liquid Argon (i.e., at 87 K), and composed of front-end mixed-signal application-specific integrated circuits (ASICs) (providing charge amplification, analog processing, digitization, compression, and a first 16:1 multiplexing), one or more digital multiplexing ASICs, and voltage regulation ASICs.

In this paper, we discuss the development of the front-end mixed-signal ASIC. In Section II, we report on the characterization of the 180 nm CMOS technology selected for the initial development, with particular attention focused on the performance in the cryogenic environment. We also introduce the concept of "1/f equivalent" and discuss the input MOSFET optimization for LAr TPC. In Section III, we present the ASIC architecture, we describe the first prototype of analog front end, which was developed using the original foundry models and parameters, we report on the first experimental results, and we introduce the 12-bit analog-to-digital converter (ADC), which will be fabricated as a separate ASIC in the development phase.

## II. CRYOGENIC CMOS

With a wire capacitance approaching 200 pF, a resolution of better than 1000 rms electrons can only be achieved if the front-end electronics are located in close proximity to the wire

ends (i.e., in the liquid Argon (87 K)). Moving the front end outside the cryogenic environment (300 K) would require, along with the additional meters of interconnect (increased capacitance and noise), a prohibitive number of feedthroughs (one or two for each of the  $\sim$ 600 000 wires). It would also make the cryostat design more complex.

In operating the CMOS technologies at the cryogenic temperature of 87 K, two critical aspects must be considered: 1) the reliability of the device models in terms of the ASIC operating point, signal response (transconductance, output resistance, and capacitance), noise, and passive components (linear resistors and capacitors), and 2) the lifetime, considering that the LAr TPC is required to operate for more than 20 years with limited access to the electronics for repair or replacement. We will report here on the former; while the latter, still being studied, will be briefly discussed at the end of this section.

As shown in Section III, we designed, fabricated, and characterized, in a commercial 180 nm CMOS technology, an analog front-end ASIC. For this first prototype, we adopted the CMOS models and parameters for room temperature provided by the foundry, and just assumed some model reliability when simulating at the cryogenic temperatures of interest. This assumption was, in part, justified by our results on the characterization of a mixed-signal 250 nm CMOS ASIC, originally developed for room temperature applications [5], and tested at temperatures down to 40 K [6]. The signal and noise responses were, to a first order, in agreement with the simulations. Along with the design of a complete analog front end, we integrated a number of test structures. In this section, we discuss the results of this characterization, which was performed at 300 K and 77 K (i.e. fully submerged in liquid nitrogen). The technology is the 180 nm CMOS from TSMC.

### A. DC Characteristics

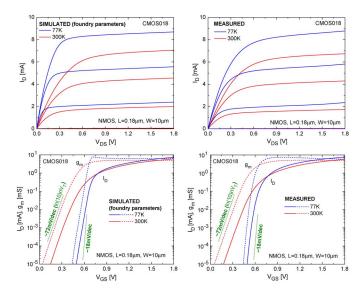

Fig. 2 shows the comparison between the simulated and measured dc characteristics of an n-channel MOSFET with a gate length L=180 nm and a gate width  $W=10~\mu\text{m}$  (five 2- $\mu\text{m}$  fingers). Very good agreement can be observed at room temperature, while some difference in the saturation voltage, subthreshold slope, and transconductance can be observed at 77 K. In Fig. 2, the subthreshold slope is expressed by using its inverse (change in gate voltage per decade of drain current), and it approaches an expected  $\ln(10) nV_t$  [7], where  $n\approx 1.3$  is the subthreshold slope factor, and  $V_t=k_BT/q$  is the thermal voltage. These results are in good agreement with others reported in the literature [8]–[10].

As discussed in Section III, the impact of these differences on the performance of our first ASIC prototype was small. However, we will consider modifying the model parameters in the next revision to better approximate the actual curves.

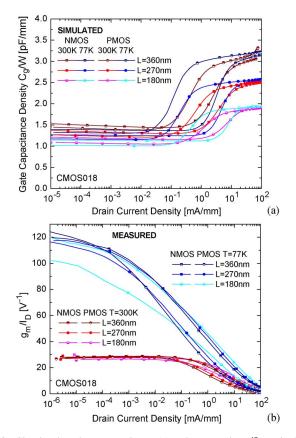

Results from the literature [9]–[12] indicate negligible dependence of the MOSFET capacitive components on the temperature. Fig. 3(a) shows the simulated dependence of the total gate capacitance on the drain current density for n- and p-channel MOSFETs at different channel lengths. For a given device, a shift in the rising edge at about three times the current density can be observed from 300 K to 77 K. The center of moderate inversion (where the inversion coefficient integrated circuit (IC)

Fig. 2. Simulated (left) and measured (right) dc characteristics of an n-channel MOSFET with  $L=180\ \text{nm}$  at  $300\ \text{K}$  (red curves) and 77 K (blue curves).

is equal to unity), which occurs at the center of the rising edge, shifts with the same factor  $\sim$ 3. The inversion coefficient IC, as derived from the EKV model [13]–[16], can be expressed as

$$IC = \frac{I_D}{2n \,\mu(T) \,C_{ox} \frac{W}{V_t^2} V_t^2} \tag{1}$$

where  $C_{ox}$  is the gate–oxide capacitance per unit area and  $\mu$  is the charge mobility, which depends on the temperature and is estimated to increase a factor  $\sim\!\!5$  from 300 K to 77 K [11], [16]. For the selected technology  $C_{ox}\approx 8.4~{\rm fF}/{\rm \mu m^2}$  and  $\mu_{300~{\rm K}}\approx 400~{\rm and}~83~{\rm cm^2V^{-1}s^{-1}}$  for n- and p-channel devices, respectively. From (1), it follows that, for a given drain current  $I_D$ , the inversion coefficient increases a factor  $\sim\!\!3$  from 300 K to 77 K. Consequently, the region of moderate inversion [14], where  $0.1 < {\rm IC} < 10$ , shifts at 77 K, about 3 times toward higher current density.

## B. Noise

With regards to the noise, we approximate the equivalent input spectral density of the MOSFET with the following operative model [17], [18] (a discussion on its origin is beyond the scope of this paper)

$$S_{V} = \frac{K_{f}(IC, L, T)}{C_{ox}WLf^{\alpha_{f}(IC, L, T)}} + \alpha_{w}(IC, L, T)n4kT\frac{\gamma(IC)}{g_{m}(IC, L, T)}$$

(2)

composed of a low-frequency term and a white term. In the low-frequency term, the amplitude coefficient  $K_f$  (joule  $\cdot$   $Hz^{\alpha_f-1}$ ) and the slope factor  $\alpha_f$  depend on the inversion coefficient IC (i.e., on drain current density), channel length L, and temperature T. Similarly, in the white term, the noise excess coefficient  $\alpha_w$  and the transconductance  $g_m$  depend on IC, L, and T. The gamma coefficient depends on the IC and can be approximated with [17]

$$\gamma = \frac{1}{1 + \mathrm{IC}} \left( \frac{1}{2} + \mathrm{IC} \frac{3}{2} \right). \tag{3}$$

Fig. 3. Simulated total gate capacitance (a) and measured  $g_{\rm m}/I_{\rm D}$  ratio (b) as functions of the drain current density  $I_{\rm D}/W$ . Red and blue curves are, respectively, for room (300 K) and liquid nitrogen (77 K) temperatures.

The  $g_m$  in (2) can be either simulated or extracted from the dc measurements. In Fig. 3(b), we show the measured ratio  $g_m/I_D$  as a function of the drain current density  $I_D/W$  for n- and p-channel MOSFETs with different channel lengths. It can be observed that as  $I_D$  decreases, the ratio  $g_m/I_D$  tends to the asymptotic value  $(nV_t)^{-1}$  which is about 30 and 115  $V^{-1}$  at 300 K and 77 K, respectively. Considering that the input MOSFET typically operates in moderate inversion, a  $g_m$  increase of about 2 at equal drain current  $I_D$  should be expected when operating at the cryogenic temperatures of interest. It follows that the white term in (2) is expected to decrease about 8 times (4 from the temperature coefficient T, 2 from the increase in  $g_m$ ), assuming no change in  $\alpha_w$ .

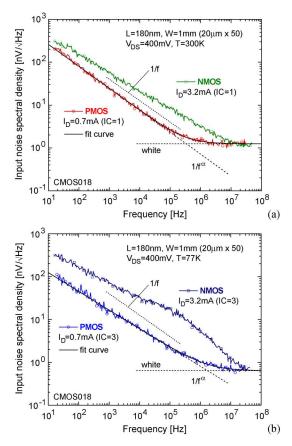

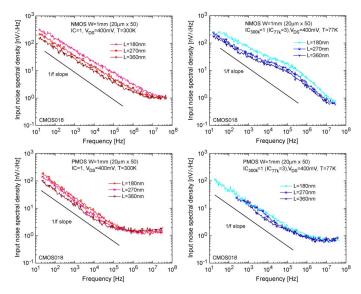

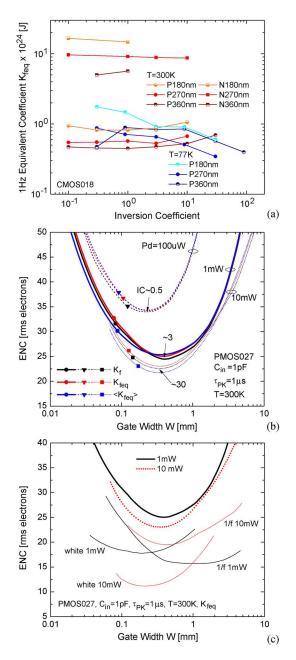

The coefficients  $\alpha_{\rm w}$ ,  $K_{\rm f}$ , and  $\alpha_{\rm f}$  must be extracted from measurements of the equivalent input noise spectral density. In Fig. 4(a), we show the measurements at 300 K on n- and p-channel MOSFETs with L = 180 nm, W = 1 mm, and IC = 1 (I<sub>D</sub> = 3.2 and 0.7 mA, respectively). While exhibiting a comparable  $K_{\rm f}$  (i.e., a comparable noise at 1 Hz), the p-channel is characterized by a higher slope (higher  $\alpha_{\rm f}$ ,  $\sim$ 1.025 compared to the  $\sim$ 0.89 of the n-channel), which makes it substantially more advantageous for low-noise applications.

The corresponding measurements at 77 K are shown in Fig. 4(b), where we biased the devices at the same drain current  $I_D$  (i.e., with  $IC \approx 3$ ). In n-channel devices, we invariably observed an increase in the region between 10 kHz and 10 MHz, which resembles a contribution from a Lorentizan packet [19]–[21] and which made impossible the extraction of the

Fig. 4. Measured equivalent input noise spectral densities at 300 K (a) and 77 K (b) on n- and p-channel MOSFETs with L = 180 nm.

white term. In *p*-channel devices, along with the expected decrease in the white term, we observed some decrease in the low-frequency component at 1 Hz (K<sub>f</sub> from  $1.084 \times 10^{-24}$  to  $0.175 \times 10^{-24}$  J) along with a decrease in the slope ( $\alpha_{\rm f}$  from 1.025 to 0.88) so that the noise value around 100 kHz was practically comparable.

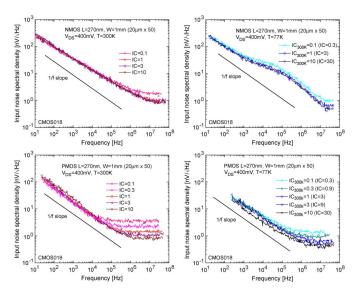

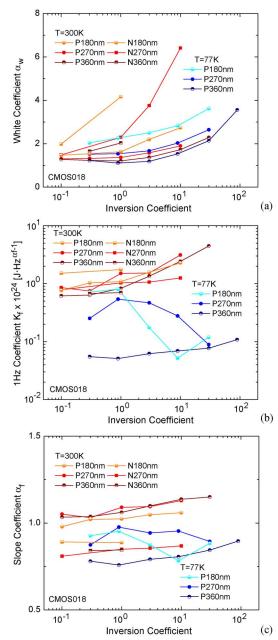

We measured the input noise spectral densities for different channel lengths and operating points (different values of drain current  $I_D$ , and drain-to-source voltage  $V_{DS}$ ). Negligible dependence on  $V_{DS}$  (above saturation) was observed at a given  $I_D$ . In Fig. 5, the measurements at 300 K and 77 K on n- and p-channel MOSFETs biased at IC=1 are shown, while Fig. 6 shows the measurements versus IC (i.e., versus ID) for the case of n- and p-channel MOSFETs with L=270 nm. Using a minimum square fitting algorithm on (2) in the  $\sim$ 1 kHz to  $\sim$ 20 MHz region, we extracted the values of  $\alpha_w$ ,  $K_f$ , and  $\alpha_f$  given in Fig. 7.

With regards to the white noise excess coefficient  $\alpha_{\rm w}$ , we extracted values larger than unity, increasing with the drain current density (i.e., with an IC). The increase was more pronounced at shorter channel lengths and it was particularly steep in n-channel devices, presumably due to electron multiplication. These results are in agreement with several others reported in the literature. See, for example, [22] and [23], where physical models are also discussed. Concerning the measurements at 77 K, as previously discussed, it was not possible to extract the coefficient for n-channel devices, while some increase with IC was observed in p-channel devices, especially at minimum channel length.

Fig. 5. Measured equivalent input noise spectral densities at 300 K (left) and 77 K (right) on n- and p-channel MOSFETs with different channel lengths and IC  $_{300~\rm K}=1~({\rm IC}_{77~\rm K}=3)$ .

Fig. 6. Measured equivalent input noise spectral densities at 300 K (left) and 77 K (right) on n- and p-channel MOSFETs with L=270 nm and different drain current densities (different values of IC).

With regards to the low-frequency noise coefficients,  $K_f$  and  $\alpha_f$ , the measurements at 300 K show an increase in  $K_f$  with the drain current density, more pronounced in p-channel devices. This seems to be in agreement with other results reported in the literature [24]–[28]. However, the increase in  $K_f$  was accompanied by a corresponding increase in the slope coefficient  $\alpha_f$  so that the low-frequency noise contribution in the 10 kHz to 100 kHz region was practically unchanged. Hence, the input MOSFET optimization process must consider both coefficients, as discussed later. Concerning the measurements at 77 K, the dependence of the  $K_f$  and  $\alpha_f$  were quite irregular, especially in the case of minimum channel length. However, also in those cases a change in  $K_f$  was accompanied by a corresponding change in the slope coefficient  $\alpha_f$ .

Fig. 7. (a) Noise coefficients  $\alpha_{\rm w}$ . (b)  ${\rm K_f}$ . (c)  $\alpha_{\rm f}$  for the model (2), extracted by using a minimum square fitting algorithm on (2) in the  $\sim 1$  kHz to  $\sim 20$  MHz from spectral measurements on n- and p-channel MOSFETs at different channel lengths and values of the inversion coefficient IC (i.e., drain current density).

### C. Equivalent Noise Charge

The expression for the equivalent noise charge (ENC) can be used to: 1) optimize the size and operating point of the input MOSFET and 2) estimate the achievable ENC. It can be modeled with [17]

$$ENC^{2} = [C_{in} + C_{gw}(IC, L, T) \cdot W]^{2}$$

$$\times \left[ \frac{a_{w}}{\tau_{p}} \frac{\alpha_{w} n \gamma(IC) 4kT}{g_{mw}(IC, L, T) \cdot W} + \frac{K_{f}(IC, L, T)}{C_{ox}WL} \right]$$

$$\times \frac{(2\pi)^{\alpha_{f}(IC, L, T)}}{\tau_{p}^{1 - \alpha_{f}(IC, L, T)}} a_{f}(\alpha_{f}(IC, L, T))$$

(4)

where  $C_{\rm in}$  is the external input capacitance, which includes the sensing wire and the interconnects, and which does not scale

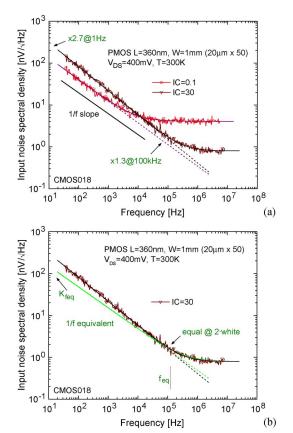

Fig. 8. (a) Comparison between noise spectral densities at  $\rm IC=0.1$  and  $\rm IC=30$  for a p-channel MOSFET with  $\rm L=360$  nm at  $\rm T=300$  K. (b) Illustration of the concept of 1/f equivalent, defined in (5) as the 1/f noise which gives a total contribution equal to the measured noise at a specific frequency  $\rm f_{eq}$  where the noise is equal to twice the white noise.

with the width W of the input MOSFET (i.e., any capacitance, including the interconnect and parasitics);  $C_{gw}$  and  $g_{mw}$  are the gate capacitance and transconductance per unit of W,  $\tau_p$  is the peaking time, and  $a_w$  and  $a_f$  are coefficients that depend on the type of shaping [17], [18], typically on the order of 1 and 0.5, respectively.

As can be observed from (4), the dependence of the  $K_f$  and  $\alpha_f$  on the bias point can make the optimization process quite cumbersome. In the next section, we discuss an alternative and simpler approach.

#### D. 1/f Equivalent

In Fig. 8(a), we consider the example of a p-channel MOSFET with L=360 nm at T=300 K. As previously discussed, to an increase in increase  $K_f$  with IC corresponds an increase in  $\alpha_f$ . For IC = 30 it follows that while the noise at 1 Hz is about 2.7 times larger, the difference is reduced to 1.3 at 100 kHz, as shown in Fig. 8(a).

We now define "1/f equivalent" the 1/f noise which gives a total contribution equal to the measured noise at a specific frequency  $f_{\rm eq},$  which is defined at the frequency where the noise density is equal to twice the white noise (a factor of four in power)

$$\begin{split} S_{veq}(f) = & \frac{K_{feq}}{C_{ox}WLf} + white \\ where & \ K_{feq} = & 3C_{ox}WLf_{eq} \times white, \ S_v(f_{eq}) = & 4 \times white \end{split} \tag{5}$$

and we define  $K_{\rm feq}$  (Joule) as "equivalent  $K_{\rm f}$ ." This concept is illustrated in Fig. 8(b) where the case IC=30 is approximated by using its 1/f equivalent. This choice can be justified considering that in most practical cases, the input MOSFET is biased at a current where the low-frequency noise slightly dominates on the white noise, while a further increase in current would result in an increase in power with only a marginal benefit in resolution.

Obviously, a dependence of the  $K_{\rm feq}$  on the operating point must be expected. However, the dependence is modest, as can be observed from Fig. 9(a), where we plot the values of the extracted  $K_{\rm feq}$ . The 1/f equivalent (i.e., the  $K_{\rm feq}$ ) can be used in the ENC equation, yielding the known

$$ENC^{2} = [C_{in} + C_{gw}(IC, L, T) \cdot W]^{2} \left[ \frac{a_{w}}{\tau_{p}} \frac{\alpha_{w} n \gamma(IC) 4kT}{g_{mw}(IC, L, T) \cdot W} + 2\pi a_{f} \frac{K_{feq}(IC, L, T)}{C_{ox}WL} \right]$$

(6)

where the expression for the low-frequency noise contribution is greatly simplified.

The impact on the MOSFET optimization process and on the ENC estimate can be appreciated from Fig. 9(b), where the ENC versus W (input MOSFET width) for  $C_{\rm in}=1$  pF and  $au_{

m p}=1~\mu{

m s}$ is shown for three different values of dissipated power: 0.1, 1, and 10 mW (dashed, solid, and dotted curves, respectively). The curves using (4) and (6) (black and red, respectively) are close, suggesting negligible error in the optimization process (optimum W) and a small error in the estimate (minimum ENC). The cases for 0.1 mW represent a situation where the white noise contribution tends to dominate, while the ones for 10 mW are for the opposite. The value of the inversion coefficient IC is also shown at the minimum ENC, ranging from 0.5 at 0.1 mW to 30 at 10 mW. As it must be expected, the benefit in increasing the dissipated power becomes eventually negligible since the low-frequency component dominates. The difference between the curves becomes more visible only in those (rare and impractical) cases where a relatively large amount of power (i.e., a large amount of mW/pF) is available. In Fig. 9(b), the curves using an "averaged 1/f equivalent" are also shown (blue curves), where a single value  $\langle K_{\rm feq} \rangle$  has been adopted, as an average value of  $K_{keq}$  versus IC from Fig. 9(a). Also in this more simplified case, the errors in optimization and estimate appear acceptable.

Intuitively, a large increase in dissipated power (i.e., a decrease in white noise) should move the optimum width W towards larger values, since white and 1/f noise contributions have a minimum for  $C_g \ll C_{\rm in}$  (typically one third when operating in strong inversion and much lower when operating in a moderate inversion [17]) and  $C_g \approx C_{\rm in}$ , respectively. As shown in Fig. 9(b), this shift does not actually occur from 1 mW to 10 mW. This can be understood by observing Fig. 9(c) where the white and 1/f noise contributions are also reported for 1 mW and 10 mW. As expected, the white contribution decreases as the power increases, but the increase with W is somewhat steeper. More relevant, the 1/f contribution shows a large dependence on the dissipated power, becoming larger as the power increases, and with the minimum shifted towards lower values of W. This

Fig. 9. (a) Plot of the coefficient  $K_{\rm feq}$  defined as in (5). (b) Impact of using  $K_{\rm feq}$  and its average  $\langle K_{\rm feq} \rangle$  on the optimization curves ENC versus W for the case of  $C_{\rm in}=1~{\rm pF},~\tau_{\rm p}=1~\mu{\rm s},$  and different values of dissipated power: 0.1 mW, 1 mW, and 10 mW. (c) White and 1/f contributions for the 1 mW and 10 mW cases at (b) by using  $K_{\rm feq}$ .

trend at large values of dissipated power is explained with the increase in the gate capacitance per unit of width W [see Fig. 3(a)].

Concerning the choice of the length L of the p-channel input MOSFET, the analysis of this technology suggests an optimum between the minimum and twice that (i.e., between 180 nm and 360 nm). For large values of milliwatts per pF, better results are achieved for L in the range 180 nm to 270 mm; for small values of milliwatts per pF, better results are achieved for L in the range of 270 nm to 360 nm. As previously discussed, the dependence of the gate capacitance per unit of width W on the drain current density plays a large role. In our case, we selected L=270 nm, as illustrated in the following section.

Fig. 10. (a) ENC veersus W for different MOSFETs at 300 K and 87 K. The dashed line represents our original simulations based on assumed values for the noise parameters; the solid lines are based on the measured values. (b) ENC versus dissipated power at T=87 K for the case of p-channel MOSFET with L=270 nm, with corresponding low-frequency and white contributions.

## E. MOSFET Optimization for LAr TPC

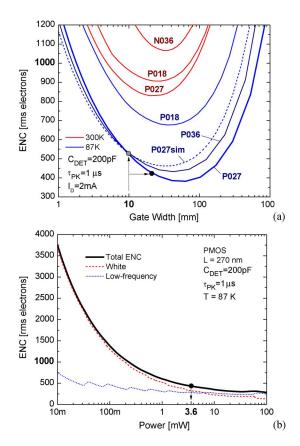

The front-end electronics for our TPC must provide, when operating in liquid Argon (87 K), a resolution better than 1000 rms electrons, with an input capacitance  $C_{\rm in}$  from the sensing wires as high as 200 pF [3]. Since the maximum input charge can approach 300 fC ( $\sim 1.9 \times 10^6$  electrons), the required dynamic range, defined as the ratio between the maximum input charge and the ENC, must exceed 2000. This imposes a constraint on the design of the filter, which will be discussed elsewhere [29].

The input MOSFET optimization is illustrated in Fig. 10 where we show the ENC versus W for different channel lengths at 300 K and 87 K (for the latter, we approximated the values of some parameters with the ones measured at 77 K) with  $I_D=2~\rm mA~(3.6~\rm mW)$  and  $\tau_{\rm p}=1~\mu \rm s$ . The dashed line represents our original simulation, based on originally assumed values for the noise parameters, while the solid lines are based on the recently acquired measured values. We selected a gate width  $W=10~\rm mm$  since, according to the original simulations, only a modest improvement (from  $\sim 530~\rm e^-$  to  $\sim 480~\rm e^-$  (i.e.,  $\sim 220~\rm e^-$ ) was to be expected for larger values of W. On the other hand, the simulations based on the measured values now indicate a larger improvement (from  $\sim 530~\rm e^-$  to  $\sim 420~\rm e^-$  (i.e.,  $\sim 320~\rm e^-$ ) if we increase W from 10 mm to 20 mm, which appears more attractive and will be implemented in the revision of the design.

The ENC versus dissipated power is shown in Fig. 10(b), along with the low-frequency and white contributions, for the case of the selected p-channel MOSFET with L=270 nm at T=87 K. We chose 3.6 mW (i.e., 2 mA), beyond which there is a diminishing return. At this operating point, the two contributions are somewhat comparable.

#### F. Lifetime

With regards to the lifetime, the major failure mechanisms, such as electromigration (EM), stress migration (SM), time-dependent dielectric breakdown (TDDB), and thermal cycling (TC) scale in favor of cryogenic operation [30], [31]. The only mechanism that can affect the lifetime at cryogenic temperature is the degradation due to impact ionization, which causes charge trapping in the MOSFET gate oxide [32].

A monitor of the impact ionization is the bulk current, which reaches a maximum at  $V_{DS} = V_{DD}$  and at  $V_{GS} \approx 0.5 V_{DD}$ . When operating constantly in this condition, the device at room temperature has a lifetime (defined as a 10% degradation in  $g_{\rm m}$ ) of about 10 years. The bulk current (i.e., the impact ionization) increases roughly a factor four at 77 K with respect to 300 K [32]. In order to guarantee the required lifetime, different design guidelines must be adopted for analog and digital circuits. The former case consists of operating the devices at moderate-to-low drain current densities, where the impact ionization is negligible. The latter case consists of operating the devices with reduced V<sub>DD</sub> (about 20%) and adopting nonminimum channel length L, considering that at cryogenic temperature, the speed of the digital circuit [33] increases, thus compensating for the increased L. We will verify these guidelines with accelerated aging tests on dedicated structures and will report the results in a future publication.

#### III. ASIC ARCHITECTURE AND ANALOG FRONT END

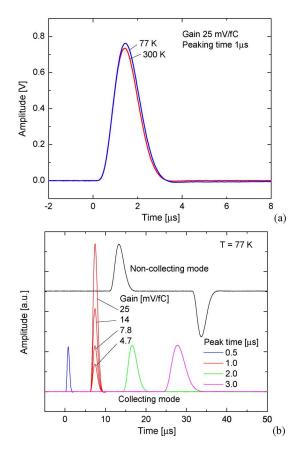

In Fig. 11, we show a block diagram of the proposed 16-channel front-end ASIC. Each channel includes a charge amplifier with adjustable gain (4.7, 7.8, 14, and 25 mV/fC, to cover, respectively, a range of 55, 100, 180, and 300 fC), a high-order antialiasing filter with an adjustable time constant (peaking time 0.5, 1, 2, 3  $\mu$ s), option to enable an ac coupling stage, baseline adjustment to 200 mV or 900 mV for operation with either the collecting or the noncollecting wires, a 12-bit 2 MSamples/s ADC, and a data compression stage.

Shared among the 16 channels are the bias circuits, registers, a temperature monitor, a pulse generator, the digital multiplexer, an analog buffer for signal monitor, and the digital interface. A 600 kbit buffer will be integrated, capable of storing up to 1.5 ms worth of event, sampled at 2 MSamples/s, in each channel and assuming no compression. Two or more events can be stored with compression. The projected layout size, pads included, is on the order of  $11 \times 6$  mm<sup>2</sup>. The expected dissipated power is below 12 mW per channel with a 1.8 V supply.

As anticipated in Section II, in the first phase, we are pursuing two separate ASIC developments: 1) the analog front-end ASIC, which has been fabricated and characterized as described

Fig. 11. (a) Block diagram and (b) simplified layout of the proposed front-end mixed-signal ASIC; the projected power dissipation is below 12 mW/channel. The projected size, pads included, is on the order of  $6\times11~\mathrm{mm}^2$ .

in the next two Sections, and 2) the ADC-buffer ASIC, which is being currently finalized. In designing both ASICs, we applied the guidelines that we expect would provide the required 20-year lifetime.

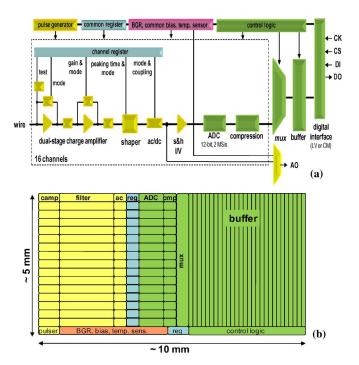

#### A. Architecture of the Analog Front-End ASIC

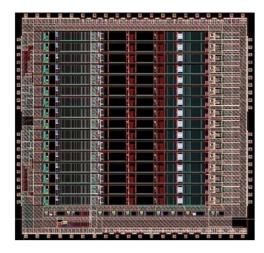

The analog ASIC consists of the front-end section down to the ac/dc coupling stage from Fig. 11(a), including the channel registers and its digital interface. The physical layout is shown in Fig. 12. Access to the individual test structures, used for the characterization reported in Section II, is at the top and bottom of the layout. The input MOSFET is a p-channels biased at 2 mA (3.6 mW) with a L/W ratio of 0.27  $\mu$ m/10 mm (200 fingers, 50  $\mu$ m each), in agreement with our conclusions in Section II, followed by a dual cascode stage [34]. At 300 K and 77 K the MOSFET offers, respectively, a  $g_{\rm m} \sim 45~{\rm mS}$  and  $\sim 90$ mS and a  $C_{\rm g}\sim 14~{\rm pF}$  and  $\sim\!18~{\rm pF}$ , operating at  $IC\sim 0.4$  and  $\sim$ 1.25 (i.e., in moderate inversion). The charge amplification is obtained in two stages, each with adaptive reset and nonlinear pole-zero cancellation [35], [36], and it provides a charge gain up to  $20 \times 16 = 320$ , adjustable to 4.7, 7.8, 14, and 25 mV/fC. The charge amplifier is followed by a high-order semi-Gaussian anti-aliasing filter [37] with adjustable time constant and the ac/dc coupling stage which, when enabled, introduces an ac a time constant on the order of 100  $\mu$ s. Each channel also implements, not shown in Fig. 11(a), a high-performance analog buffer capable of driving 250  $\Omega$ //400 pF and which, in the final version, will be replaced with the sample-and-hold stage preceding the ADC [see Fig. 11(a)]. The buffer will still be used for monitoring the analog signals. In its current version, the

Fig. 12. Physical layout of the analog ASIC, with size  $\sim 6 \times 6 \text{ mm}^2$ .

analog ASIC is suitable for a possible integration in the Micro-Boone LAr TPC detector [38]. The dissipated power is about 5 mW/channel, plus an additional ~5 mW in each output buffer.

The ASIC integrates a band-gap reference (BGR), used to generate all of the internal bias voltages and currents (as ratios between the BGR voltage and a resistor). With a modest dependence of the non-silicided resistors with the temperature (a few percent from 300 K to 77 K, in line with our preliminary results reported in the next section), this bias scheme offers good stability of the operating points over a wide range of temperatures.

In designing the ASIC, the operating points were set to absorb the shifts with the temperature of the MOSFET thresholds (see Fig. 2). The use of voltage feedback configurations with high loop gains and passive feedback components made it possible to contain the dependence on the temperature of the signal response.

## B. Preliminary Experimental Results

The ASIC, encapsulated in a standard plastic package, was characterized at room temperature (300 K) and fully submerged in liquid nitrogen (77 K). The text fixture was placed in a dewar and the liquid nitrogen was poured in a few seconds until the fixture was fully submerged. During these tests, the fixture was cycled, without incurring in any issue, more than 50 times between the two environments.

Fig. 13 shows the measured pulse response, along with some details on the adjustment of the gain, peaking time, and baseline. These results are in close agreement with our simulations and indicate that the analog and the digital circuits (including the digital interface) operate as expected in the cryogenic environment. Simulations and experimental results show that the nonlinear pole-zero cancellation at cryogenic temperature needs to be optimized, which will be done in the next revision of the design. The revision will also integrate the test structures for the characterization of the CMOS lifetime and the temperature dependence of the non-silicided resistors.

Charge Sensitivity Calibration: Each channel is equipped with an injection capacitor of nominal value 198 fF (size  $10 \times 18 \ \mu m^2$ ) which can be used for test and calibration and can be

Fig. 13. Measured pulse response at 300 K and 77 K (a), with details (b) on the adjustment of gain, peak time, and baseline.

enabled and disabled through a dedicated internal register. By using a precisely measured external capacitor, we extracted the value of the injection capacitance, equal to 184 fF at 300 K and 183 fF at 77 K, with a change of less than 0.5%. This remarkable result, along with the small change in peaking time with the temperature [Fig. 13(a)], demonstrates a high stability of the passive components (resistors and capacitors). In reference to the band-gap reference circuit, we measured 1.185 V at 300 K and 1.164 V at 77 K, with a decrease of about 1.8 %. The temperature sensor gave 867 mV at 300 K and 259.3 mV at 77 K, with a response of 2.86 mV/K, in close agreement with the simulations as well.

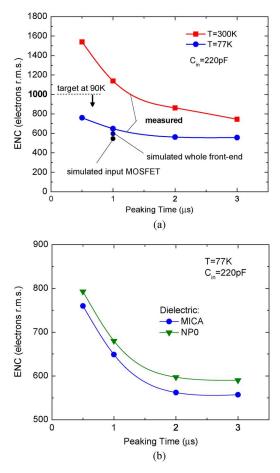

Fig. 14 shows the measured ENC versus the time constant (peaking time) of the entire analog chain (preamplifier, filter, buffer). At 1  $\mu s$ , we measured  $\sim 650~e^-$ , to be compared to the simulated  $\sim 530~e^-$  in Fig. 10. If we include in the simulation the contributions from the next stages in the analog chain, we obtain  $\sim 600~e^-$ . The residual difference is due to the thermal noise from the  $\sim 12~\Omega$  (3  $\Omega$  at 77 K) parasitic resistance of the ASIC input lines, which contributes to about 150 e^-. The width of those lines will be increased in the revision in order to reduce it to negligible. A second contribution, on the order of 60 e^-, is due to the dielectric loss from the input capacitor used to simulate the wire, which can be approximated with [39]

$$ENC_{diel} \approx \sqrt{2kTC_{diel} \cdot tg(\delta)}$$

(7)

Fig. 14. (a) Measured ENC for the analog ASIC at 300 K and 77 K at the four peaking times. The simulated ENC from the input MOSFET and from the whole analog chain is also shown. (b) Measured ENC using a MICA and a ceramic NPO capacitor to emulate the sense wire capacitance.

where  $tg(\delta)$  is the dielectric loss factor. In Fig. 14(b), we compare the measurements by using MICA and NPO ceramic capacitors, exhibiting dielectric loss at  $77~{\rm K} \sim 0.1 \times 10^{-3}$  and  $2.5 \times 10^{-3}$ , respectively. It is worth noting that the dielectric loss contribution will not be present with the wire.

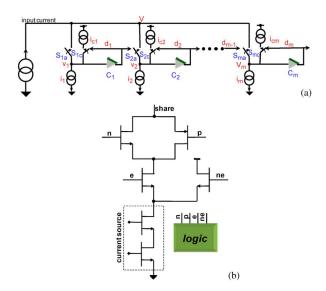

#### C. Architecture of the ADC

The shaped signal which results from the induction in the TPC wires must be sampled and digitized in 12-bit words at a rate of 2 MSamples/s. This is achieved by integrating one ADC in each channel. The ADC, currently being finalized as a separate ASIC, aims at offering the 12-bit resolution, converting in less than 500 ns, and dissipating about 2 mA (3.6 mW). In our design, the power can be reduced at the expense of the conversion time, which scales approximately with the inverse of the current.

The conversion occurs in two stages, the first requiring about 150 ns and providing the six most significant bits (MSBs); and the second requiring about 250 ns and providing the six least-significant bits (LSBs), for a total of 12 bits resolution in about 400 ns. The residual 100 ns are available for encoding and reset.

Both stages (LSB and MSB) are based on the current mode ADC concept described in [34] where the input voltage is sampled, converted into a current, and compared with a number of

Fig. 15. Simplified schematic of the (a) ADC architecture and (b) individual ADC cell.

matched current cells sequentially enabled. Fig. 15(a) shows a simplified schematic of the ADC structure. The individual cell is shown in Fig. 15(b) and it is composed of a cascoded current source, two MOSFETs controlled by signals e and ne, and providing current steering with positive feedback, two other MOSFETs controlled by signals n and p and working as switches, and a control logic. The layout size is about 1.2  $\rm mm \times 230~\mu m$ . Details on the design and layout, along with the experimental results, will be published later.

## ACKNOWLEDGMENT

The authors would like to thank M. Stanacevic from Stony Brook University for helpful discussions, J. D. Cressler from the Georgia Institute of Technology, and to our colleagues at Fermi National Laboratory: R. Yarema, G. Deptuch, and J. Hoff. The authors would also like to thank A. Kandasamy for invaluable CAD tools assistance and J. Triolo and D. Pinelli for expert technical assistance. The reviewers, Editor, and Senior Editor provided very valuable feedback as always.

#### REFERENCES

- [1] Long Baseline Neutrino Experiment. (2011). [Online]. Available: http://lbne.fnal.gov/

- [2] The US Long Baseline Neutrino Experiment Study. (2007). [Online]. Available: http://www.bnl.gov/isd/documents/41139.pdf

- [3] V. Radeka, H. Chen, G. Deptuch, G. De Geronimo, F. Lanni, S. Li, N. Nambiar, S. Rescia, C. Thorn, R. Yarema, and B. Yu, "Cold electronics for giant liquid Argon time projection chambers," in *Proc. 1st Int. Workshop Towards the Giant Liquid Argon Charge Imaging Experiment* [Online]. Available: http://iopscience.iop.org/1742-6596, to be published in the *Journal of Physics*, Conference Series

- [4] The ICARUS 50 I LAr TPC in the CERN v BEAM. (2006). [Online]. Available: http://cdsweb.cern.ch/record/435493/files/9812006.pdf

- [5] G. De Geronimo, J. Fried, E. Frost, B. F. Phlips, E. Vernon, and E. A. Wulf, "Front-end ASIC for a Silicon Compton telescope," *IEEE Trans. Nucl. Sci.*, vol. 55, no. 4, pp. 2323–2328, Aug. 2008.

- [6] H. Chen, G. De Geronimo, J. Fried, F. Lanni, D. Makowiecki, V. Radeka, S. Rescia, and E. Vernon, "Cryogenic readout electronics R&D for MicroBoone and beyond," *Nucl. Instrum. Meth.*, vol. A623, pp. 391–393, 2010.

- [7] P. R. Gray, P. J. Hurst, S. H. Lewis, and R. G. Meyer, Analysis and Design of Analog Integrated Circuits, 4th ed. New York: Wiley, 2001, pp. 66–67.

- [8] A. Akturk, M. Holloway, S. Potbhare, D. Gundlach, B. Li, N. Goldsman, M. Peckerar, and K. P. Cheung, "Compact and distributed modeling of cryogenic bulk MOSFET operation," *IEEE Trans. Electron. Devices*, vol. 57, no. 6, pp. 1334–1342, Jun. 2010.

- [9] D. Foty, "An evaluation of deep-submicron CMOS design optimized for operation at 77 K," *Analog Integr. Circ. Sig. Process*, vol. 49, pp. 97–105, 2006.

- [10] S. Venkataraman, B. Banerjee, C.-H. Lee, J. Laskar, and J. D. Cressler, "Cryogenic small signal operation of 0.18 μm MOSFETs," in *Proc. IEEE Topical Meeting on Silicon Monolithic Integrated Circuits in RF Systems*, Long Beach, CA, 2007, pp. 52–55.

- [11] G. Ghibaudo and F. Balestra, "Low temperature characterization of silicon CMOS devices," in *Proc. 20th Int. Conf. Microelectron.*, 1995, vol. 2, pp. 613–622.

- [12] P. Martin, M. Cavelier, R. Fascio, G. Ghibaudo, and M. Bucher, "EKV3 compact modeling of MOS transistors from a 0.18 μm CMOS technology for mixed analog-digital circuit design at low temperature," *Cryogenics*, vol. 49, no. 11, pp. 595–598, 2009.

- [13] C. C. Enz and E. A. Vittoz, "MOS transistor modeling for low-voltage and low-power analog IC design," *Microelectron. Eng.*, vol. 39, pp. 59–76, 1997.

- [14] D. M. Colombo, G. I. Wirth, and C. Fayomi, "Design methodology using inversion coefficient for low-voltage low-power CMOS voltage reference," in *Proc. 23rd Symp. Integr. Circuits Syst. Design*, 2010, pp. 43–48.

- [15] N. D. Arora and G. S. Gildenblat, "A semi-empirical model of the MOSFET inversion layer mobility for low-temperature operation," *IEEE Trans. Electron. Devices*, vol. 34, no. 1, pp. 89–93, Jan. 1987.

- [16] D. M. Binkley, "Tradeoffs and optimization in analog CMOS design," IEEE Trans. Electron. Devices, vol. ED-34, no. 1, pp. 89–93, Jan. 1987.

- [17] G. De Geronimo and P. O'Connor, "MOSFET optimization in deep submicron technology for charge amplifiers," *IEEE Trans. Nucl. Sci.*, vol. 52, no. 6, pt. 2, pp. 3223–3232, Dec. 2005.

- vol. 52, no. 6, pt. 2, pp. 3223–3232, Dec. 2005.

[18] G. De Geronimo, "Low noise electronics for radiation sensors," in *Medical Imaging: Principles, Detectors, and Electronics*, K. Iniewski, Ed. Hoboken, NJ: Wiley, 2009.

- [19] C. Hu, G. P. Li, E. Worley, and J. White, "Consideration of low-frequency noise in MOSFETs for analog performance," *IEEE Electron. Devices Lett.*, vol. 17, no. 12, pp. 552–554, Dec. 1996.

- [20] G. O. Workman and J. G. Fossum, "Physical noise modeling of SOI MOSFET's with analysis of the Lorentzian component in the low-frequency noise spectrum," *IEEE Trans. Electron. Devices*, vol. 47, no. 6, pp. 1192–1201, Jun. 2000.

- [21] F. C. Hou, G. Bosman, and M. E. Law, "Simulation of oxide trapping noise in submicron n-channel MOSFETs," *IEEE Trans. Electron. Devices*, vol. 50, no. 3, pp. 846–852, Mar. 2003.

- [22] R. P. Jindal, "Compact noise models for MOSFETs," *IEEE Trans. Electron. Devices*, vol. 53, no. 9, pp. 2051–2061, Sep. 2006.

- [23] S. Choudhary and S. Qureshi, "Input noise modeling of deep submicron MOSFETs," in *Proc. Microelectron. Optoelectron. Conf.*, 2007, pp. 175–179.

- [24] E. P. Vandamme and L. K. J. Vandamme, "Critical discussion on unified 1 = f noise models for MOSFETs," *IEEE Trans. Electron. Devices*, vol. 47, no. 11, pp. 2146–2152, Nov. 2000.

- [25] M. Valenza, A. Hoffmann, D. Sodini, A. Laigle, F. Martinez, and D. Rigaud, "Overview of the impact of downscaling technology on 1/f noise in p-MOSFETs to 90 nm," *Proc. Inst. Elect. Eng. Circuits Devices Syst.*, vol. 151, no. 2, pp. 102–110, 2004.

- [26] M. Manghisoni, L. Ratti, V. Re, V. Speziali, and G. Traversi, "Noise performance of 0.13 μm CMOS technologies for detector front-end applications," *IEEE Trans. Nucl. Sci.*, vol. 53, no. 4, pt. 2, pp. 2456–2462, Aug. 2006.

- [27] G. Bertuccio and S. Caccia, "Noise Minimization of MOSFET input charge amplifiers based on  $\Delta\mu$  and  $\Delta N$  1/f models," *IEEE Trans. Nucl. Sci.*, vol. 56, no. 3, pp. 1511–1520, Jun. 2009.

- [28] L. Ratti, M. Manghisoni, V. Re, and G. Traversi, "Design optimization of charge preamplifiers with CMOS processes in the 100 nm gate length regime," *IEEE Trans. Nucl. Sci.*, vol. 56, no. 1, pp. 235–242, Feb. 2009.

- [29] G. De Geronimo and S. Li, "Shaper design in CMOS for high dynamic range," *Nucl. Instrum. Meth.*, submitted for publication.

- [30] J. Srinivasan, S. V. Adve, P. Bose, and J. A. Rivers, "The impact of technology scaling on lifetime reliability," in *Proc. IEEE Int. Conf. De*pendable Systems and Networks, Jun. 2004, pp. 177–186.

- [31] J. Qin and J. B. Bernstein, "Non-Arrhenius temperature acceleration and stress-dependent voltage acceleration for semiconductor device involving multiple failure mechanisms," in *Proc. IEEE Int. Integr. Rel. Workshop*, 2003, pp. 93–97.

- [32] T. Chen, L. Najafizadeh, C. Zhu, A. Ahmed, R. Diestelhorst, G. Espinel, and J. D. Cressler, "CMOS device reliability for emerging cryogenic space electronics applications," in *Proc. IEEE Int. Semiconduct. Device Res. Symp.*, 2005, pp. 328–329.

- [33] Y. Feng, P. Zhou, H. Liu, J. Sun, and T. Jiang, "Characterization and modeling of MOSFET operating at cryogenic temperature for hybrid superconductor-CMOS circuits," *Semicond. Sci. Technol.*, vol. 19, no. 1, pp. 1381–1385, 2004.

- [34] G. De Geronimo, J. Fried, G. C. Smith, B. Yu, E. Vernon, C. L. Britton, W. L. Bryan, L. G. Clonts, and S. S. Frank, "ASIC for small angle neutron scattering experiments at SNS," *IEEE Trans. Nucl. Sci.*, vol. 54, no. 3, pp. 541–548, Jun. 2007.

- [35] G. De Geronimo and P. O'Connor, "A CMOS detector leakage current self-adaptable continuous reset system: Theoretical analysis," *Nucl. In-strum. Meth.*, vol. A421, pp. 322–333, 1999.

- [36] G. De Geronimo, J. Fried, P. O'Connor, V. Radeka, G. C. Smith, C. Thorn, and B. Yu, "Front-end ASIC for a GEM based time projection chamber," *IEEE Trans. Nucl. Sci.*, vol. 51, no. 4, pp. 1312–1317, Aug. 2004.

- [37] S. Okhawa, M. Yoshizawa, and K. Husimi, "Direct synthesis of the Gaussian filter for nuclear pulse amplifiers," *Nucl. Instrum. Meth.*, vol. 138, pp. 85–92, 1976.

- [38] MicroBooNE Document 185. (2007). [Online]. Available: http://microboone=docdb.fnal.gov/cgi-bin/DocumentDatabase

- [39] G. De Geronimo, P. O'Connor, and J. Grosholz, "A generation of CMOS readout ASICs for CZT detectors," *IEEE Trans. Nucl. Sci.*, vol. 47, no. 6, pp. 1857–1867, Dec. 2000.