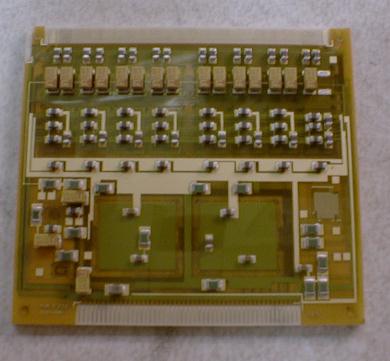

| Shown in the picture on the right is the MCM in question. It measures 48x43 mm, which is about 2/3 of a credit card, and services 256 silicon strips or pads. The Silicon signals will arrive at the top. What is visible is mostly surface-mount capacitors. The top half holds 2 rows of 8 chips: 32-channel AMU-ADC's, followed by 32-channel ADC's. Under the large green squares in the foreground are the 2 Xilinx FPGA's, and along the bottom of the MCM are 50 traces for communication to and from the outside world. |

|

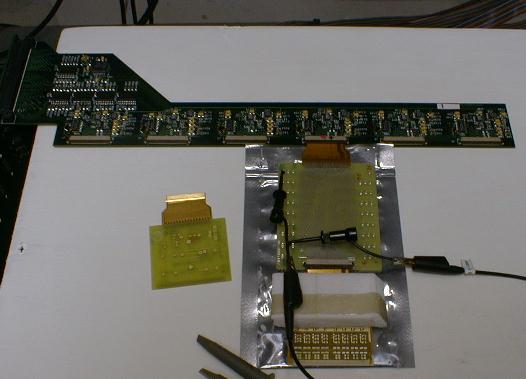

| This is a view of the test setup. Part of the MCM is visible at the

bottom of the picture. Wirebonds connect it to a short output cable. Since the

bonds have not yet been encapsulated, they are covered up with the white foam

protector.

Between the MCM output cable and the Power/Communication board along the top of the picture is a temporary board which allows us to look at the communications to/from the MCM. |

|

There seems to be an offset (one bit) we think in the serial string alignment. We believe we know where this comes from and it is easily fixed in software.

We have not done any serious signal/noise tests.