## ALICE ITS POWER SYSTEM 32-CHANNEL VERSION

# **OPERATION MANUAL V1.6**

This manual is meant for use with prototype production power board v1.1 (labelled v1) and v1.2 (labelled v1.1)

LAWRENCE BERKELEY NATIONAL LABORATORY - NUCLEAR SCIENCE DIVISION

# CONTENTS

| 2                                                                                                         |                         | History2-                                           |            |                                                                                    | 2-3      |

|-----------------------------------------------------------------------------------------------------------|-------------------------|-----------------------------------------------------|------------|------------------------------------------------------------------------------------|----------|

| 3                                                                                                         |                         | Introduction3-                                      |            |                                                                                    |          |

| 4                                                                                                         | Content of the package4 |                                                     |            |                                                                                    |          |

| 5                                                                                                         |                         | Pow                                                 | ver bo     | ard                                                                                | 5-6      |

| 6                                                                                                         |                         | Breakout board                                      |            |                                                                                    | 6-9      |

|                                                                                                           | 6.                      | 6.1 General description                             |            |                                                                                    | 6-9      |

|                                                                                                           | 6.                      | 2                                                   | Elect      | trical and timing characteristics                                                  | 6-12     |

|                                                                                                           |                         | 6.2.                                                | 1          | Power in connectors (3.3V) - Pin characteristics                                   | 6-12     |

|                                                                                                           |                         | 6.2.                                                | 2          | Power in connector (-5V) - Pin characteristics                                     | 6-12     |

|                                                                                                           |                         | 6.2.<br>MO                                          | 3<br>SAIC) | I2C connector - Pin characteristics (Valid only for connection to RUv1 – skip 6-13 | this for |

| 7                                                                                                         |                         | Asse                                                | emblii     | ng the power system                                                                | 7-15     |

|                                                                                                           | 7.                      | 1                                                   | Sing       | le module testing setup                                                            | 7-15     |

|                                                                                                           |                         | 7.1.                                                | 1          | Powering the power board using a power supply (default configuration)              | 7-15     |

|                                                                                                           |                         | 7.1.                                                | 2          | Powering via a VME crate (requires front panel mechanics - not yet availab         | le)7-17  |

|                                                                                                           | 7.                      | 7.2 Endurance tests/Stave testing recommended setup |            |                                                                                    | 7-19     |

|                                                                                                           |                         | Endurance tests: output power/bias connections      |            |                                                                                    | 7-21     |

|                                                                                                           |                         | 7.2.                                                | 1          | Stave testing: output power/bias connections                                       | 7-22     |

| 8                                                                                                         |                         | I2C                                                 | transa     | actions                                                                            | 8-23     |

| 9                                                                                                         |                         | Оре                                                 | erating    | g the system                                                                       | 9-24     |

|                                                                                                           | 9.                      | 1                                                   | Setti      | ing a temperature threshold                                                        | 9-24     |

|                                                                                                           | 9.                      | 2                                                   | Setti      | ing the current thresholds                                                         | 9-25     |

|                                                                                                           | 9.                      | 3                                                   | Adju       | sting the output voltages                                                          | 9-26     |

|                                                                                                           | 9.                      | 4                                                   | Setti      | ng the bias voltages                                                               | 9-27     |

|                                                                                                           | 9.                      | 5                                                   | Enat       | bling supply and bias channels                                                     | 9-28     |

|                                                                                                           | 9.                      | 6                                                   | Cheo       | king remotely the status of the power outputs                                      | 9-30     |

| 9.7 Monitoring the output voltages and currents                                                           |                         | itoring the output voltages and currents            | 9-32       |                                                                                    |          |

| 9.7.1 Resistance of traces from the output of the regulators to the wire connection on the breakout board |                         |                                                     | •          |                                                                                    |          |

|                                                                                                           | 9.                      | 8                                                   | Mon        | itoring the temperature of the system                                              | 9-36     |

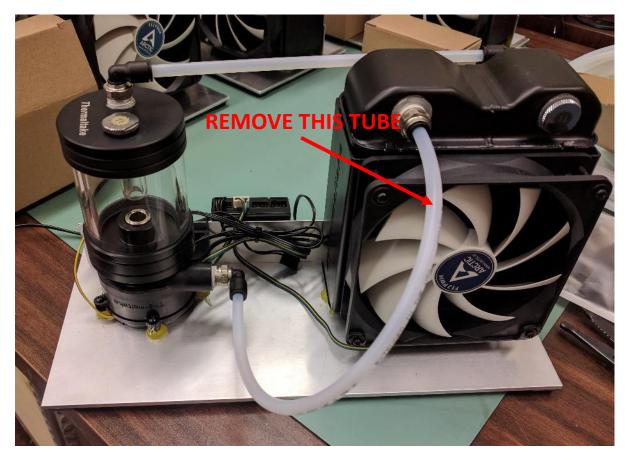

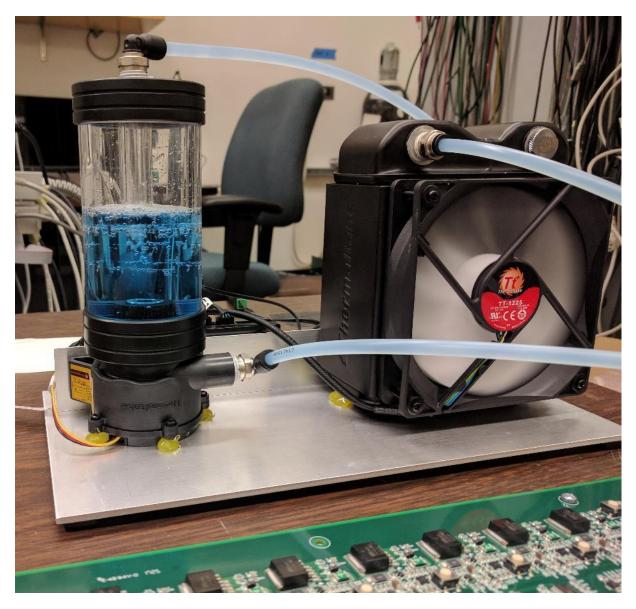

| 1(                                                                                                        | )                       | Ir                                                  | nstalla    | tion of the stand-alone cooling system                                             | 10-37    |

|                                                                                                           | 10                      | D.1                                                 | Asse       | mbly of the system                                                                 | 10-38    |

| Contacts |

|----------|

|----------|

# 2 HISTORY

12/6/2017 – A. Collu - Released first draft of the Operation Manual (v1.0)

3/7/2017 – A. Collu – Added section on how to assemble the power system, reviewed breakout board section, applied minor corrections (v1.1)

14/7/2017 – A. Collu – Added table containing trace resistances (v1.2)

14/09/2017 – L. Greiner – Added section on stand-alone cooling system installation and operation (v1.3)

3/7/2018 – A. Collu – Fixed wrong cross references and reformatted section 10 on the stand-alone cooling system (v1.4)

4/9/2018 – A. Collu – Modified sequence of commands to configure the ADCs to increase conversion rate (v1.5)

12/10/2018 – A. Collu – Fixed typo found in the command to read out the ADC channels (v1.6)

# **3** INTRODUCTION

This manual provides the specifications of the ALICE ITS power system – 32-channel version, a description of its functionalities and guidelines to its operation.

The ALICE power system is composed of a power board where a basic set of functionalities is implemented and of two breakout boards that serve as physical adapters to connect the power board to up to 16 sensor modules.

This system can generate 32 nominally 1.8V power supply voltages - one analog supply voltage and one digital supply voltage per module - each providing drive strength up to 3A, and 16 additional negative voltages with low current strength that can be used to bias the sensor modules.

The main features of the power generation system, addressable via standard I2C interfaces (see specifications in section 6.2.3), are summarized below:

- Individual enabling of supply and bias voltages

- Individual adjustment of supply voltages

- Adjustment of bias voltages on a power unit (8-channel basis)

- Over-current protection circuits with adjustable thresholds on each supply voltage

- Over-temperature protection circuits with manually adjustable thresholds for each 16channel power unit.

- Monitoring features (voltage / current / temperature)

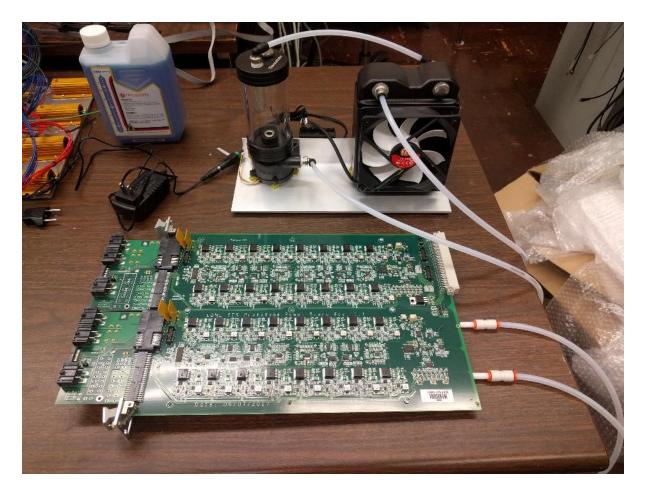

In order to dissipate the heat generated during normal operation, the main power board is equipped with a heat exchanger (true only for endurance tests/stave testing power boards) which needs to be connected to a liquid based cooling system (see Section 10 or information on how to cool the power board). Due to their low dissipated power, individual module testing power boards do not need to use an external cooling system. For this reason these power boards will not come with a heat exchanger. It is intended that this power system be used in conjunction with the MOSAIC readout board developed by Bari for the testing of modules/staves for the ALICE ITS Upgrade.

The latest version of this manual can be found at:

https://twiki.cern.ch/twiki/pub/ALICE/Documentation/2018\_10\_12\_ITS\_power\_system\_V16\_32channel\_operation\_manual.docx

Other functionalities added to the board with the purpose of testing alternative system configurations (e.g. control over VME bus) will not be described in this manual.

# **4 CONTENT OF THE PACKAGE**

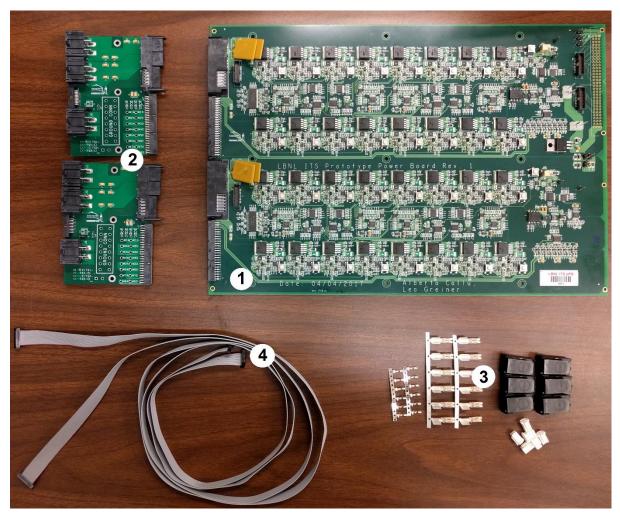

<image>

The power system comes in a package that contains the following items\* (

### Figure 1):

- 1) 1 x Power Board (VME 6U x 340mm) with a heat exchanger on its back\*\*

- 2) 2 x Breakout Board (7cm x 103.5cm)

- 3) mating connectors, pins and jumpers (items and item quantity may differ from shown)

- 4) 2 x 20-pin ribbon cable SAMTEC FFSD-10-D-40.00-01-N cable (length ~1m)

- 1 x liquid cooling system (will be delivered to endurance tests/stave testing sites, not shown in the picture)

Figure 1: Content of the package (quantity for each part may be different than shown)

\*Quantity for some of the items may exceed minimum required.

\*\*Please note that this version of the power board will not fit a 1 unit VME slot of the specified dimensions (thickness is not compatible with 1 unit size). Heat exchanger may not be provided (e.g. single module testing power boards).

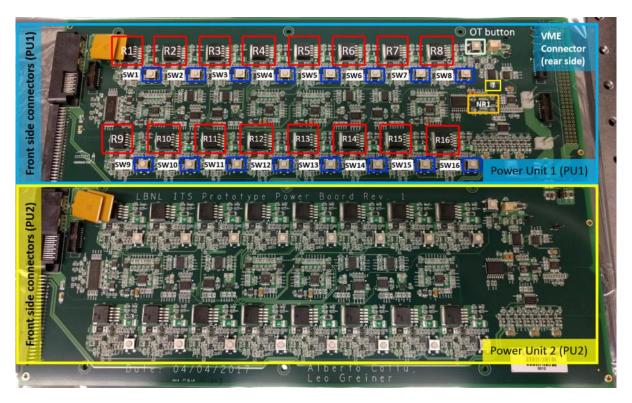

# 5 POWER BOARD

The power board (Figure 2) consists of two fully independent and functionally identical half boards or Power Units (PU). Each power unit is split into two polyfuse-protected power domains referenced to a common ground plane. Jumpers on the power board allow for different powering/grounding configurations. The input power may be provided to each domain either from the front of the power board via a breakout board or from the rear side of the power board via a VME connector (only possible for single module testing power boards, see section 7.1).

Each power unit contains a set of 16 positive voltage regulators powered at 3.3V (R\* in Figure 2, 8 per power domain) which are used to generate digital and analog supply voltages to the modules. One negative voltage regulator (NR1 in Figure 2) plus a set of 8 FET switches per power unit generate 8 additional low-current voltages to bias up to 8 sensor modules.

All the functionalities implemented on the power board can be accessed via I2C interfaces (the two power units have independent interfaces). A set of push buttons (SW\* in Figure 2) allows each supply channel to be enabled manually for test purposes.

A heat exchanger, positioned on the back of the board (not shown), may be connected to an external cooling system (see Section ...). The temperature of each power unit can be monitored (see Subsection 9.8) using a PT100 temperature sensor (T in figure).

Figure 2: Power Board

A total of 66 LEDs indicate the status of various parts of the board and can help identifying possible issues (See Table 1 for power unit 1 and Table 2 for power unit 2), in particular:

- A red LED near each regulator is used to indicate the occurrence of an overcurrent condition.

When this happens, the corresponding channel is automatically switched off. At board power on all these red LEDs are turned on indicating that all supply voltages are grounded.

- 2) A green LED located near each regulator is used to indicate that the corresponding channel is enabled and working properly. Since its brightness grows with the magnitude of the output voltage, it may not be visible for low output voltage values (below 1.8V). Green LED and red LED belonging to the same channel cannot be simultaneously on. The happening of such condition is an indication that the board is not working properly.

- 3) A red LED located on the right (back) side of each power unit is used to indicate the occurrence of an over-temperature condition (temperature threshold is set to 70°C by default). When this happens all the supply channels of that power unit are disabled simultaneously. To recover from an over-temperature condition it is necessary that the OT button located on the rear side of the power unit is pressed (works only if power unit temperature is below threshold). Alternatively, the power unit can be power cycled.

| LED ID | Description                                                              |  |  |

|--------|--------------------------------------------------------------------------|--|--|

| D35    | Module 1 analog voltage is enabled                                       |  |  |

| D1     | Module 1 analog voltage is disabled (at power up and after overcurrent)  |  |  |

| D36    | Module 1 digital voltage is enabled                                      |  |  |

| D3     | Module 1 digital voltage is disabled (at power up and after overcurrent) |  |  |

| D37    | Module 2 analog voltage is enabled                                       |  |  |

| D5     | Module 2 analog voltage is disabled (at power up and after overcurrent)  |  |  |

| D38    | Module 2 digital voltage is enabled                                      |  |  |

| D4     | Module 2 digital voltage is disabled (at power up and after overcurrent) |  |  |

| D39    | Module 3 analog voltage is enabled                                       |  |  |

| D9     | Module 3 analog voltage is disabled (at power up and after overcurrent)  |  |  |

| D40    | Module 3 digital voltage is enabled                                      |  |  |

| D6     | Module 3 digital voltage is disabled (at power up and after overcurrent) |  |  |

| D41    | Module 4 analog voltage is enabled                                       |  |  |

| D8     | Module 4 analog voltage is disabled (at power up and after overcurrent)  |  |  |

| D42    | Module 4 digital voltage is enabled                                      |  |  |

| D7     | Module 4 digital voltage is disabled (at power up and after overcurrent) |  |  |

| D43    | Module 5 analog voltage is enabled                                       |  |  |

| D13    | Module 5 analog voltage is disabled (at power up and after overcurrent)  |  |  |

| D44    | Module 5 digital voltage is enabled                                      |  |  |

| D10    | Module 5 digital voltage is disabled (at power up and after overcurrent) |  |  |

| D45    | Module 6 analog voltage is enabled                                       |  |  |

| D12    | Module 6 analog voltage is disabled (at power up and after overcurrent)  |  |  |

### Table 1: Description of Power Unit 1 status LEDs

| D46                                     | Module 6 digital voltage is enabled                                      |

|-----------------------------------------|--------------------------------------------------------------------------|

| D11                                     | Module 6 digital voltage is disabled (at power up and after overcurrent) |

| D47                                     | Module 7 analog voltage is enabled                                       |

| D17                                     | Module 7 analog voltage is disabled (at power up and after overcurrent)  |

| D48 Module 7 digital voltage is enabled |                                                                          |

| D14                                     | Module 7 digital voltage is disabled (at power up and after overcurrent) |

| D49                                     | Module 8 analog voltage is enabled                                       |

| D16                                     | Module 8 analog voltage is disabled (at power up and after overcurrent)  |

| D50                                     | Module 8 digital voltage is enabled                                      |

| D15                                     | Module 8 digital voltage is disabled (at power up and after overcurrent) |

| D2                                      | Power Unit 1 over-temperature condition has occurred                     |

### Table 2: Description of Power Unit 2 status LEDs

| LED ID | Description                                                              |  |

|--------|--------------------------------------------------------------------------|--|

| D51    | Module 1 analog voltage is enabled                                       |  |

| D21    | Module 1 analog voltage is disabled (at power up and after overcurrent)  |  |

| D52    | Module 1 digital voltage is enabled                                      |  |

| D18    | Module 1 digital voltage is disabled (at power up and after overcurrent) |  |

| D53    | Module 2 analog voltage is enabled                                       |  |

| D20    | Module 2 analog voltage is disabled (at power up and after overcurrent)  |  |

| D54    | Module 2 digital voltage is enabled                                      |  |

| D19    | Module 2 digital voltage is disabled (at power up and after overcurrent) |  |

| D55    | Module 3 analog voltage is enabled                                       |  |

| D25    | Module 3 analog voltage is disabled (at power up and after overcurrent)  |  |

| D56    | Module 3 digital voltage is enabled                                      |  |

| D22    | Module 3 digital voltage is disabled (at power up and after overcurrent) |  |

| D57    | Module 4 analog voltage is enabled                                       |  |

| D24    | Module 4 analog voltage is disabled (at power up and after overcurrent)  |  |

| D58    | Module 4 digital voltage is enabled                                      |  |

| D23    | Module 4 digital voltage is disabled (at power up and after overcurrent) |  |

| D59    | Module 5 analog voltage is enabled                                       |  |

| D29    | Module 5 analog voltage is disabled (at power up and after overcurrent)  |  |

| D60    | Module 5 digital voltage is enabled                                      |  |

| D26    | Module 5 digital voltage is disabled (at power up and after overcurrent) |  |

| D61    | Module 6 analog voltage is enabled                                       |  |

| D28    | Module 6 analog voltage is disabled (at power up and after overcurrent)  |  |

| D62    | Module 6 digital voltage is enabled                                      |  |

| D27    | Module 6 digital voltage is disabled (at power up and after overcurrent) |  |

| D63    | Module 7 analog voltage is enabled                                       |  |

| D33    | Module 7 analog voltage is disabled (at power up and after overcurrent)  |  |

| D64    | Module 7 digital voltage is enabled                                      |  |

| D30    | Module 7 digital voltage is disabled (at power up and after overcurrent) |  |

| D65    | Module 8 analog voltage is enabled                                       |  |

| D32    | Module 8 analog voltage is disabled (at power up and after overcurrent)  |  |

| D66    | Module 8 digital voltage is enabled                                      |  |

| D31    | Module 8 digital voltage is disabled (at power up and after overcurrent) |  |

| D14    | Power Unit 2 over-temperature condition has occurred                     |  |

# 6 BREAKOUT BOARD

### 6.1 GENERAL DESCRIPTION

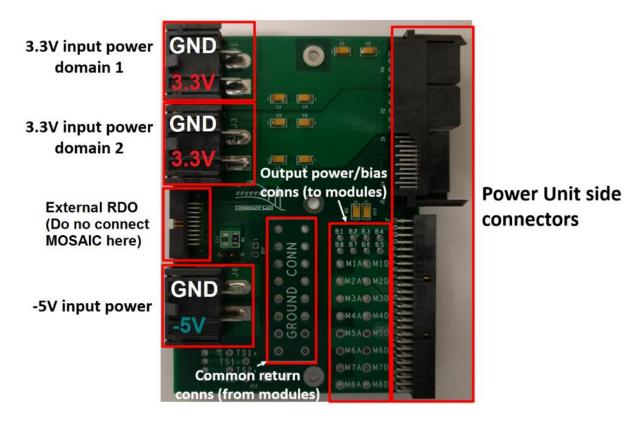

The breakout board (Figure 3) is an interface board that connects to a power unit on the power board. It has the following main purposes:

- 1) Provide power to the two positive power domains of a power unit

- 2) Provide power to the bias section of a power unit

- 3) Provide a physical interface between an external readout system and a power unit (connector J4, Samtec SHF-110-01-L-D-RA type). Note that the MOSAIC board is not compatible with the pinout of this connector on the breakout board and will need to be connected directly to dedicated connectors on the power board (J72 on power unit 1 and J75 on power unit 2).

- 4) Provide a physical interface between the power unit and the sensor modules. In particular it allows for the soldering of wires that bring power/bias to the modules.

On the top side of the breakout board (Figure 3), 3 MOLEX 172043-0202 connectors (J1, J3 and J6) are placed which bring 2 nominally 3.3V voltages (3.3V input power for domain 1 and 2) and a nominally -5V voltage to generate the bias voltages for the modules.

Figure 3: Detailed picture of the top side of the breakout board

A Samtec SHF-110-01-L-D-RA connector is also placed on top of the board that allows the power unit to interface to an external readout system (not intended for use with MOSAIC, only with RUv1).

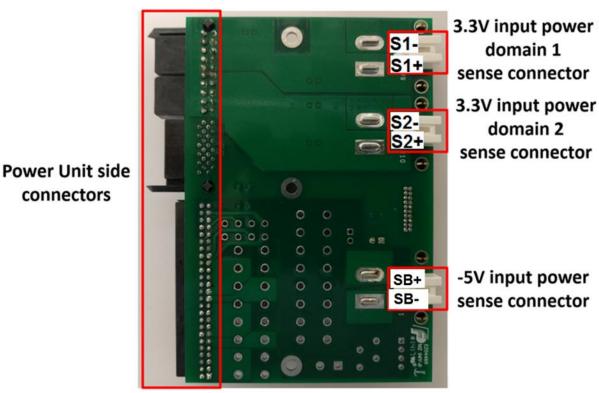

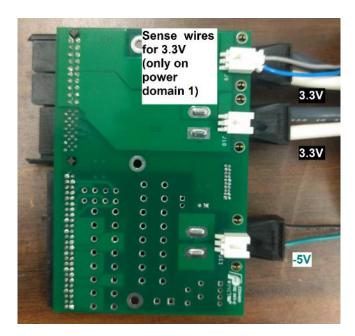

On the bottom of the breakout board, underneath the input power connectors, 3 MOLEX 53426-0210 connectors are located that are used to for attaching the sense wires that go to the 3.3V and -5V power supplies. In this way, the voltage at each power input of the breakout board can be kept constant regardless of current consumption.

Figure 4: Detailed picture of the bottom side of the breakout board

Cables for powering the power board (3.3V and -5V) are not provided. However pins and mating connectors are provided for all the input connectors (See section 7 for details on how to build these cables). Table 4 gives recommendations for wire sizes to use for input power and sense wires.

#### Table 3: Recommended wire sizes for input power/sense cables

| Description             | Wire AWG (Section [mm <sup>2</sup> ]) |

|-------------------------|---------------------------------------|

| 3.3V (power and return) | 10 (5.26)                             |

| -5V (power and return)  | 10 (5.26)                             |

| sense wires for 3.3V    | 22 (0.326)                            |

| sense wires for -5V     | 22 (0.326)                            |

A total of 16 power, 16 return and 8 bias connections (M\*A, M\*D, GROUND CONN, B\*) allow for the soldering of wires to interface to up to 8 sensor modules (see recommendations for max wire sizes for the various connections in Table 4.

| Label | Description                  | Wire Min AWG (Max Section [mm <sup>2</sup> ]) |  |

|-------|------------------------------|-----------------------------------------------|--|

| M1A   | Analog voltage for Module 1  | 16 (1.31)                                     |  |

| M1D   | Digital voltage for Module 1 | 16 (1.31)                                     |  |

| M2A   | Analog voltage for Module 2  | 16 (1.31)                                     |  |

| M2D   | Digital voltage for Module 2 | 16 (1.31)                                     |  |

| M3A   | Analog voltage for Module 3  | 16 (1.31)                                     |  |

| M3D   | Digital voltage for Module 3 | 16 (1.31)                                     |  |

| M4A   | Analog voltage for Module 4  | 16 (1.31)                                     |  |

| M4D   | Digital voltage for Module 4 | 16 (1.31)                                     |  |

| M5A   | Analog voltage for Module 5  | 16 (1.31)                                     |  |

| M5D   | Digital voltage for Module 5 | 16 (1.31)                                     |  |

| M6A   | Analog voltage for Module 6  | 16 (1.31)                                     |  |

| M6D   | Digital voltage for Module 6 | 16 (1.31)                                     |  |

| M7A   | Analog voltage for Module 7  | 16 (1.31)                                     |  |

| M7D   | Digital voltage for Module 7 | 16 (1.31)                                     |  |

| M8A   | Analog voltage for Module 8  | 16 (1.31)                                     |  |

| M8D   | Digital voltage for Module 8 | 16 (1.31)                                     |  |

| B1    | Bias voltage for Module 1    | 20 (0.518)                                    |  |

| B2    | Bias voltage for Module 2    | 20 (0.518)                                    |  |

| B3    | Bias voltage for Module 3    | 20 (0.518)                                    |  |

| B4    | Bias voltage for Module 4    | 20 (0.518)                                    |  |

| B5    | Bias voltage for Module 5    | 20 (0.518)                                    |  |

| B6    | Bias voltage for Module 6    | 20 (0.518)                                    |  |

| B7    | Bias voltage for Module 7    | 20 (0.518)                                    |  |

| B8    | Bias voltage for Module 8    | 20 (0.518)                                    |  |

### 6.2 ELECTRICAL AND TIMING CHARACTERISTICS

This section provided the voltage specifications, current ratings, pinout and timing characteristics of the breakout board interfaces.

### 6.2.1 Power in connectors (3.3V) - Pin characteristics

#### Table 5: Pin functions and recommended operating conditions for 3.3V connectors\* (applies to J1, J3 on breakout board)

|            | Description | Recommended Operating Conditions |       |

|------------|-------------|----------------------------------|-------|

| Pin Number | Description | Min                              | Max   |

| 1          | +3.3V       | +3.3V                            | +3.6V |

| 2          | GND         | -                                | -     |

\*For best performance it is suggested that sense wires be used on each 3.3V power domain

#### Table 6: Current ratings for 3.3V connectors

| Current        | Description            | Мах                                        |

|----------------|------------------------|--------------------------------------------|

| I <sub>1</sub> | +3.3V sourcing current | 10A (protected by PTC fuse on power board) |

| l <sub>2</sub> | GND sinking current    | 30A (Unprotected)                          |

### Table 7: Pin functions for 3.3V sense connectors (applies to J9 and J10 on breakout board)

| Pin Number | Description |  |

|------------|-------------|--|

| 1          | + sense     |  |

| 2          | - sense     |  |

### 6.2.2 Power in connector (-5V) - Pin characteristics

Table 8: Pin functions and recommended operating conditions for -5V connectors (applies to J1 and J3 on breakout board)

| Die Number | Description | Recommended Operating Conditions |       |

|------------|-------------|----------------------------------|-------|

| Pin Number |             | Min                              | Max   |

| 1          | -5V         | -4.5V                            | -5.5V |

| 2          | GND         | -                                | -     |

#### Table 9: Current ratings for -5V connector

| Current        | Description          | Max                                         |

|----------------|----------------------|---------------------------------------------|

| I <sub>1</sub> | -5V sinking current  | 1.1A (protected by PTC fuse on power board) |

| l <sub>2</sub> | GND sourcing current | 30A (Unprotected)                           |

#### Table 10: Pin functions for -5V sense connector (applies to J11)

| Pin Number | Description |

|------------|-------------|

| 1          | - sense     |

| 2          | + sense     |

# 6.2.3 I2C connector - Pin characteristics (Valid only for connection to RUv1 – skip this for MOSAIC)

| Pin Num | I2C ch | Name                          | Description        | Туре             | Direction |

|---------|--------|-------------------------------|--------------------|------------------|-----------|

| 1       | Main   | SDA1_WRITE_N <sup>1</sup>     | I2C data in line   | Differential (N) | Input     |

| 2       | Main   | SDA1_WRITE_P <sup>1</sup>     | I2C data in line   | Differential (P) | Input     |

| 3       | Main   | SCL1_WRITE_N <sup>1</sup>     | I2C clock in line  | Differential (N) | Input     |

| 4       | Main   | SCL1_WRITE_P <sup>1</sup>     | I2C clock in line  | Differential (P) | Input     |

| 5       | -      | GND <sup>2</sup>              | External ground    | -                | -         |

| 6       | -      | GND <sup>2</sup>              | External ground    | -                | -         |

| 7       | Main   | SCL1_READ_N <sup>1</sup>      | I2C clock out line | Differential (N) | Output    |

| 8       | Main   | SCL1_READ_P <sup>1</sup>      | I2C clock out line | Differential (P) | Output    |

| 9       | Main   | SDA1_READ_N <sup>1</sup>      | I2C data out line  | Differential (N) | Output    |

| 10      | Main   | SDA1_READ_P <sup>1</sup>      | I2C data out line  | Differential (P) | Output    |

| 11      | Aux    | SDA1_AUX_WRITE_N <sup>1</sup> | I2C data in line   | Differential (N) | Input     |

| 12      | Aux    | SDA1_AUX_WRITE_P <sup>1</sup> | I2C data in line   | Differential (P) | Input     |

| 13      | Aux    | SCL1_AUX_WRITE_N <sup>1</sup> | I2C clock in line  | Differential (N) | Input     |

| 14      | Aux    | SCL1_AUX_WRITE_P <sup>1</sup> | I2C clock in line  | Differential (P) | Input     |

| 15      | -      | GND <sup>2</sup>              | External ground    | -                | -         |

| 16      | -      | GND <sup>2</sup>              | External ground    | -                | -         |

| 17      | Aux    | SCL1_AUX_READ_N <sup>1</sup>  | I2C clock out line | Differential (N) | Output    |

| 18      | Aux    | SCL1_AUX_READ_P <sup>1</sup>  | I2C clock out line | Differential (P) | Output    |

| 19      | Aux    | SDA1_AUX_READ_N <sup>1</sup>  | I2C data out line  | Differential (N) | Output    |

| 20      | Aux    | SDA1_AUX_READ_P <sup>1</sup>  | I2C data out line  | Differential (P) | Output    |

#### Table 11: Pin functions (applies to J4 on breakout board)

Note 1: The SDA and SCL bidirectional data line of the I2C protocol are split into two mono-directional lines (SDA\*\_READ and SCL\*\_WRITE).

Note 2: Pin 5, 6, 15 and 16 (all shorted together on the breakout board) must be connected to an external ground reference if AC or DC ground coupling via the breakout board is required. In such case a jumper must be placed on header J5 on the breakout board and values of capacitor C11 and resistor R1 on the breakout board may need to be reviewed to optimize coupling characteristics.

#### Table 12: Recommended operating conditions for differential input pins

| Voltage level       | Description                                    | Min    | Max     |

|---------------------|------------------------------------------------|--------|---------|

| ΔV <sub>IN</sub>    | Magnitude of differential input voltage        | 0.050V | +3.3V   |

| V <sub>ABS-IN</sub> | Absolute voltage at any differential input pin | -1.4V  | +3.8V   |

| ΔV <sub>HYST</sub>  | Differential input voltage hysteresis          | 0V     | +0.025V |

#### Table 13: Specifications for differential output pins

| Voltage level        | Description                                     | Min    | Max    |

|----------------------|-------------------------------------------------|--------|--------|

| <b>ΔV</b> out        | Magnitude of the differential output voltage    | +0.48V | +0.65V |

| V <sub>ABS-OUT</sub> | Absolute voltage at any differential output pin | GND    | +2V    |

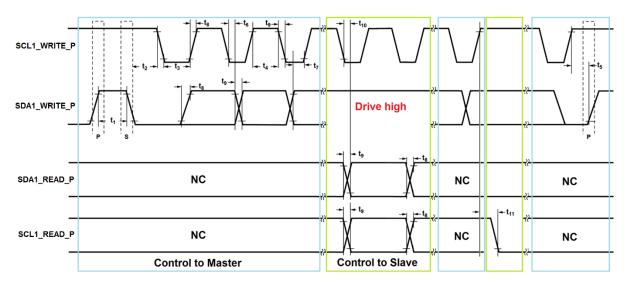

| Table 14: Timing characteristics breakout board I2C interfaces (specified for signals SDA1_*_P and SCL1_*_P of "main" |

|-----------------------------------------------------------------------------------------------------------------------|

| I2C interface, equivalent specifications for type N signals and for "aux" interface)                                  |

| Name                    | Description                                                  | Min   | Max    |

|-------------------------|--------------------------------------------------------------|-------|--------|

| <b>f</b> <sub>SCL</sub> | I2C clock frequency                                          | -     | 100kHz |

| t1                      | Bus-Free Time between Stop and Start                         | 4.7us | -      |

| t2                      | SCL1_WRITE_P Hold time for start and repeated start          | 4us   | -      |

| t₃                      | Low period of SCL1_WRITE_P                                   | 4.7us | -      |

| t <sub>4</sub>          | High period of SCL1_WRITE_P                                  | 4.0us | -      |

| t₅                      | SCL1_WRITE_P setup time for stop                             | 4us   | -      |

| t <sub>6</sub>          | SDA1_WRITE_P hold time                                       | 0     | -      |

| t7                      | SDA1_WRITE_P setup time (also setup time for repeated start) | 250ns | -      |

| t <sub>8</sub>          | SDA1_WRITE_P and SCL1_WRITE_P rise time                      | -     | 1us    |

| t9                      | SDA1_WRITE_P and SCL1_WRITE_P fall time                      | -     | 300ns  |

| t <sub>10</sub>         | SCL1_WRITE_P fall to SDA1_READ_P output (clock-to-output)    |       | 3.45us |

| t <sub>11</sub>         | SCL1_WRITE_P rise to SCL1_READ_P low (clock stretching)      | 0     | 1us    |

Note1: Differential input data signals (SCL1\_READ and SDA1\_WRITE) must be actively driven high in the high state.

Figure 5: Timing diagram for SCL1\_\*\_P and SDA1\_\*\_P lines (S = Start condition, P = Stop condition)

# 7 ASSEMBLING THE POWER SYSTEM

### 7.1 SINGLE MODULE TESTING SETUP

Single module testing stations will need to operate only two nominally 1.8V supply channels (1 digital and 1 analog voltage) and one bias channel on power unit 1. No cooling is required for this configuration. The connection scheme to external power supplies and configuration of the jumpers on the power board depends on whether a 6U is used as main source of power for the power board or if a standard power supply is used for this purpose. The following sections describe how to assemble the system in the two configurations.

### 7.1.1 Powering the power board using a power supply (default configuration)

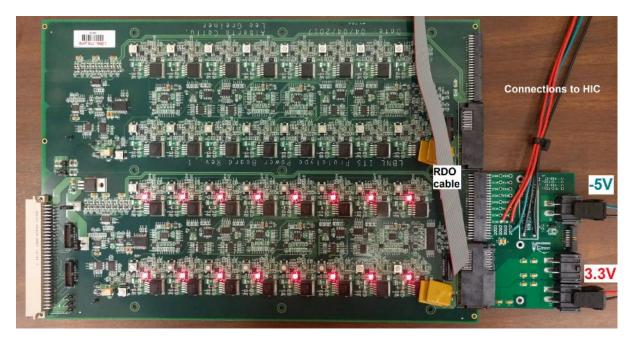

Figure 6 shows how to configure the power for single module testing when a 6U VME crate is not available (wire size shown in the picture may be different than required, picture is meant for representation only). Sensing is not required if input power wire sizes are as specified in section 6.1. The following material is required:

- Two power supplies (5V/3A for the 3.3V and 5V/0.5A for the -5V, not provided)

- 1 x Breakout Board

- 2 x black connector (2-pin Molex 172672-2002 type)

- 4 x pins for the black connectors (Molex 171825-0100 type)

- 1 x readout cable (20-pin Samtec FFSD-10-D-40.00-01-N) for the connection to MOSAIC

- 2 x 0.2" jumper

- 4 x 1m-long wires for the input power to the power board (not provided)

- 5 x 1m-long wires (specs to be agreed with characterisation group) for output power and bias voltages to the modules (not provided)

Figure 6: Power board connections for single module testing without a VME crate

The user will be required to:

- 1) Build two power cables (one for the 3.3V voltage and one for the -5V voltage)

- 2) Solder 5 wires (for power to modules) on a breakout board (3 wires on M1A, M1D, B1 and 2 wires on "GROUND CONNS")

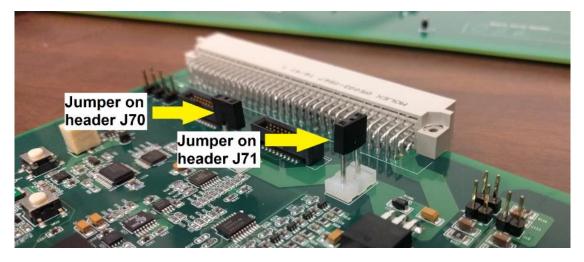

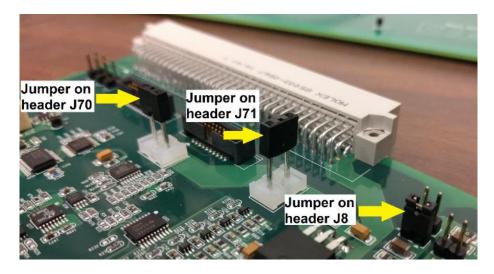

- 3) Load a 0.2" jumper on header J70 and another 0.2" jumper on header J71 (see Figure 7)

- 4) Connect the readout cable from MOSAIC to connector J72 on power unit 1

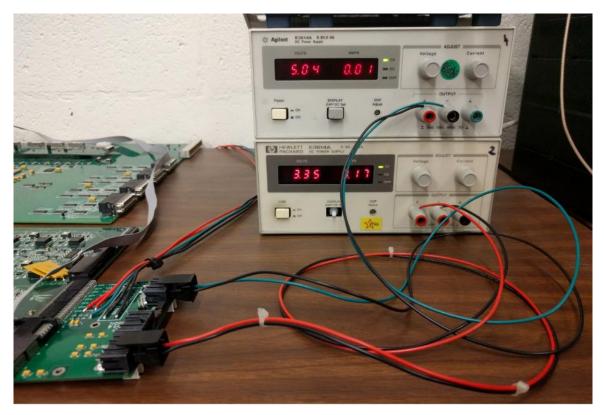

- 5) Connect each power cable to the corresponding power supply as shown in Figure 8. It is not required that the "+" side of the power supply for the -5V is shorted to the "-" side of the power supply for the 3.3V, since this connection is established by the breakout board.

Figure 7: Power board jumper configuration without a 6U VME crate (single module testing only)

Figure 8: Power supply connections to the breakout board - No VME crate configuration (single module testing only)

### 7.1.2 Powering via a VME crate (requires front panel mechanics – not yet available)

Figure 9 shows how to configure the power for single module testing when a 6U VME crate is available (wire size shown in the picture may be different than required, this is meant for representation only). Sensing is not required if the size of the input power wires is as specified in section 6.1. The following material is required:

- 6U VME crate (3 or more slots must be available) and one power supply (5V/0.5A), not provided

- 1 x Breakout Board

- 1 x black connector (2-pin Molex 172672-2002 type)

- 2 x pins for the two black connector (Molex 171825-0100 type)

- 1 x readout cable (Samtec FFSD-10-D-40.00-01-N) for the connection to the MOSAIC board

- 2 x 0.2" jumper

- 1 x 0.1" jumper

- 2 x 1m-long wires for the input power to the power board (not provided)

- 5 x 1m-long wires (?) for output power and bias voltages to the modules (not provided)

Figure 9: Power board connections for single module testing with a VME crate

The user will be required to:

- 1) Build a power cable for the -5V voltage

- 2) Solder 5 wires (for power to modules) on a breakout board (3 wires on M1A, M1D, B1 and 2 wires on "GROUND CONN")

- 3) Load a 0.2" jumper on header J70 and another 0.2" jumper on header J71 (see Figure 10)

- 4) Load a 0.1" jumper on header (see Figure 10)

- 5) Connect the readout cable from MOSAIC to connector J72

- 6) Plug the power board in the VME crate and connect the power cable to the power supply that provides the -5V (Figure 11). It is not required that the "+" side (black cable) of this power supply be connected to the ground of the VME crate, since this connection is established by the power board if jumper J8 is in place.

Figure 10: Power board jumper configuration with VME (single module testing only)

Figure 11: Power board powered via a VME crate (not a 6U crate, picture is for representation only).

### 7.2 ENDURANCE TESTS/STAVE TESTING RECOMMENDED SETUP

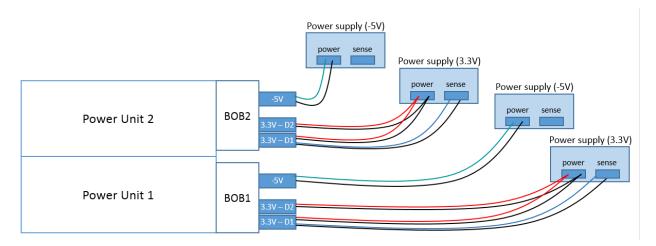

Multiple module testing stations (endurance tests or stave testing stations) will need to operate up to 14 channels per power unit. These stations require the use of active cooling as shown in Figure 12 and sense wires (not shown in Figure 12). VME crates cannot be used to provide power to the board. The following material is required (per power unit):

- Two power supplies (see specifications in the next sections, not provided)

- 1 x Breakout Board

- 3 x black connector (2-pin Molex 172672-2002 type)

- 6 x pin for the three black connectors (Molex 171825-0100 type)

- 1 x white connector (2-pin Molex 51103-0200 type)

- 2 x pins for white connector (Molex 50351-8000 type)

- 1 x readout cable (Samtec FFSD-10-D-40.00-01-N) for the connection to the MOSAIC board

- 6 x 1m-long wires for the input power (not provided)

- 2 x 1m-long wires for the sense connections to the 3.3V input voltage (not provided)

- Up to 35 x 1m-long wires (?) for output power and bias voltages to each module (not provided and not shown in the picture)

Figure 12: Endurance tests/stave testing power board configuration. Wire connections to modules not shown for simplicity.

The user will be required to (per power board):

- 1) Build 6 power cables (1 for the -5V and 2 for the 3.3V per power unit)

- 2) Build 2 sense cables (1 for the 3.3V per power unit)

- 3) Solder up to 35 wires on each breakout board (see next section for recommended configurations)

- 4) Make sure that no jumpers are present on the power board

- 5) Connect the readout cables from MOSAIC to connectors J72 (on power unit 1) and connector J75 (on power unit 2)

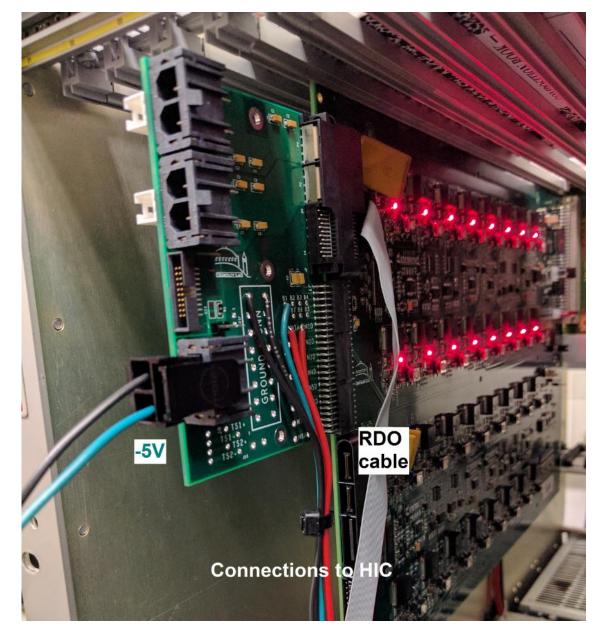

- 6) Connect each power and sense cable to the corresponding power supply (see Figure 13 for the scheme of connection and Figure 14 for an implementation):

- a) Connect two 3.3V power cables on each breakout board (a power supply will provide 3.3V to both breakout board domains)

- b) Connect a sense cable to the sense connector for 3.3V power domain 1 on each breakout board (see section 6.1 for pin polarity).

Figure 13: Configuration for power/sense wires at the input of the breakout boards

Figure 14: power unit sense wire configuration for endurance tests/stave testing

### Endurance tests: output power/bias connections

Endurance tests require 10 modules to be powered at the same time. The 3.3V input voltages to a power unit can be provided by the same power source (suggested power supply: 5V/10A with sense connection). An additional power supply per power unit is required for the input voltage to the bias circuitry (5V/1A). To minimize offsets and avoid overvoltage it is required that each power unit power 5 modules. In each power unit 3 modules may be powered via power domain 1 and 2 modules via power domain 2. This leads to the powering scheme represented in Table 15 for power and bias connections (for the ground connections, 10 wires per breakout board need to be soldered in the "GROUND CONN" island).

| Breakout Board # | Wire Connection Label on Breakout Board | Connections to modules       |

|------------------|-----------------------------------------|------------------------------|

| 1                | M1A                                     | Module 1 Analog connection   |

|                  | M1D                                     | Module 1 Digital connection  |

|                  | B1                                      | Module 1 Bias connection     |

|                  | M2A                                     | Module 2 Analog connection   |

|                  | M2D                                     | Module 2 Digital connection  |

|                  | B2                                      | Module 2 Bias connection     |

|                  | M3A                                     | Module 3 Analog connection   |

|                  | M3D                                     | Module 3 Digital connection  |

|                  | B3                                      | Module 3 Bias connection     |

|                  | M5A                                     | Module 4 Analog connection   |

|                  | M5D                                     | Module 4 Digital connection  |

|                  | B5                                      | Module 4 Bias connection     |

|                  | M6A                                     | Module 5 Analog connection   |

|                  | M6D                                     | Module 5 Digital connection  |

|                  | B6                                      | Module 5 Bias connection     |

| 2                | M1A                                     | Module 6 Analog connection   |

|                  | M1D                                     | Module 6 Digital connection  |

|                  | B1                                      | Module 6 Bias connection     |

|                  | M2A                                     | Module 7 Analog connection   |

|                  | M2D                                     | Module 7 Digital connection  |

|                  | B2                                      | Module 7 Bias connection     |

|                  | M3A                                     | Module 8 Analog connection   |

|                  | M3D                                     | Module 8 Digital connection  |

|                  | B3                                      | Module 8 Bias connection     |

|                  | M5A                                     | Module 9 Analog connection   |

|                  | M5D                                     | Module 9 Digital connection  |

|                  | B5                                      | Module 9 Bias connection     |

|                  | M6A                                     | Module 10 Analog connection  |

|                  | M6D                                     | Module 10 Digital connection |

|                  | B6                                      | Module 10 Bias connection    |

#### Table 15: Module connection scheme for endurance tests

### 7.2.1 Stave testing: output power/bias connections

Stave testing requires up to 14 modules to be powered at the same time. The 3.3V voltages to a power unit can be provided by the same power source (suggested power supply: 5V/15A with sense connection). An additional power supply per power unit is required for the input voltage to the bias circuitry (5V/1A). To minimize offsets and avoid overvoltage it is suggested that each power unit power a half stave (7 modules in an outer layer half stave). In each power unit, 4 half stave modules may be powered via power domain 1 and 3 half stave modules via power domain 2. This leads to the scheme represented in Table 16 for power and bias connections (14 ground connections per breakout board need to be soldered in the ""GROUND CONN" island).

| Breakout Board # | Wire Connection Label on Breakout Board | Half stave/module connections |

|------------------|-----------------------------------------|-------------------------------|

| 1                | M1A                                     | HS1/Mod1 Analog connection    |

|                  | M1D                                     | HS1/Mod1 Digital connection   |

|                  | B1                                      | HS1/Mod1 Bias connection      |

|                  | M2A                                     | HS1/Mod2 Analog connection    |

|                  | M2D                                     | HS1/Mod2 Digital connection   |

|                  | B2                                      | HS1/Mod2 Bias connection      |

|                  | M3A                                     | HS1/Mod3 Analog connection    |

|                  | M3D                                     | HS1/Mod3 Digital connection   |

|                  | B3                                      | HS1/Mod3 Bias connection      |

|                  | M4A                                     | HS1/Mod4 Analog connection    |

|                  | M4D                                     | HS1/Mod4 Digital connection   |

|                  | B4                                      | HS1/Mod4 Bias connection      |

|                  | M5A                                     | HS1/Mod5 Analog connection    |

|                  | M5D                                     | HS1/Mod5 Digital connection   |

|                  | B5                                      | HS1/Mod5 Bias connection      |

|                  | M6A                                     | HS1/Mod6 Analog connection    |

|                  | M6D                                     | HS1/Mod6 Digital connection   |

|                  | B6                                      | HS1/Mod6 Bias connection      |

|                  | M7A                                     | HS1/Mod7 Analog connection    |

| -                | M7D                                     | HS1/Mod7 Digital connection   |

|                  | В7                                      | HS1/Mod7 Bias connection      |

| 2                | M1A                                     | HS2/Mod1 Analog connection    |

|                  | M1D                                     | HS2/Mod1 Digital connection   |

|                  | B1                                      | HS2/Mod1 Bias connection      |

|                  | M2A                                     | HS2/Mod2 Analog connection    |

|                  | M2D                                     | HS2/Mod2 Digital connection   |

|                  | B2                                      | HS2/Mod2 Bias connection      |

|                  | M3A                                     | HS2/Mod3 Analog connection    |

|                  | M3D                                     | HS2/Mod3 Digital connection   |

|                  | B3                                      | HS2/Mod3 Bias connection      |

|                  | M4A                                     | HS2/Mod4 Analog connection    |

|                  | M4D                                     | HS2/Mod4 Digital connection   |

|                  | B4                                      | HS2/Mod4 Bias connection      |

|                  | M5A                                     | HS2/Mod5 Analog connection    |

|                  | M5D                                     | HS2/Mod5 Digital connection   |

|                  | В5                                      | HS2/Mod5 Bias connection      |

|                  | M6A                                     | HS2/Mod6 Analog connection    |

|                  | M6D                                     | HS2/Mod6 Digital connection   |

|                  | B6                                      | HS2/Mod6 Bias connection      |

|                  | M7A                                     | HS2/Mod7 Analog connection    |

|                  | M7D                                     | HS2/Mod7 Digital connection   |

|                  | В7                                      | HS2/Mod7 Bias connection      |

### Table 16: Module connection scheme for stave testing

# 8 I2C TRANSACTIONS

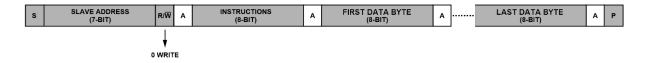

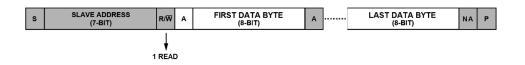

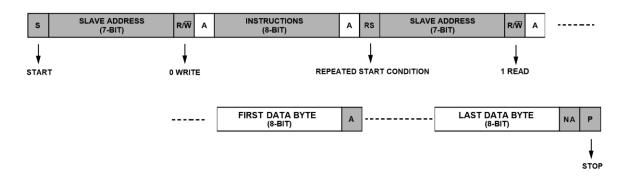

As mentioned previously, each power unit is equipped with a Samtec SHF-110-01-L-D-SM connector that allows it to interface to an external readout system. This connector carries the signals for two I2C interfaces with data (SDA) and clock (SCL) lines implemented as separate (mono-directional) read and write channels (SDA\_WRITE and SDA\_READ, see Paragraph 6.2.3 for electrical specifications). The following lines illustrate how transactions are performed through one of these interfaces.

Each transaction is always initiated by the external board and can be of three types represented Figure 15, Figure 16 and Figure 17 (write, read and read with repeated start). Each x-bit field represented in any table or figure in the following sections is intended to be transmitted/received with the most significant bit going out/coming in first.

Figure 15: I2C write transaction (Grey = control to Master, White = control to Slave, S = Start, A = ACK, P = Stop)

Figure 17: I2C read transaction with repeated start (Grey = control to Master, White = control to Slave, RS = rep start)

The following sections describe the I2C transactions that are required to operate a power unit. Commands are for power unit 1 but equivalent commands may be used for power unit 2.

# **9 O**PERATING THE SYSTEM

### 9.1 Setting a temperature threshold

An over-temperature mechanism is implemented in the system that switches off power to the regulators in case the temperature of the heat exchanger exceeds a default threshold of 70°C. Upon power on of the board this mechanism is disabled. In order to enable it is necessary to bias the on-board temperature sensor performing an I2C write transaction to the "I2C main interface" of the target power unit as shown in Table 17 (start, acknowledge and stop bits are not reported).

Table 17: Write transaction to bias the temperature sensor used by the over-temperature circuit (all values are binary)

| Trans type | Slave address + R/V | V bit | Instruction 1 | Instruction 2 | Data byte     |

|------------|---------------------|-------|---------------|---------------|---------------|

| write      | 0101000             | 0     | 0000001       | 1000000       | 1100001[FREQ] |

The 1-bit FREQ field must be set high if the frequency of the mains power system is 50Hz, zero otherwise.

The default threshold may be modified by acting on trimmer R1135 (R1136 on power unit2, see Figure 18). This causes the voltage on test point J4 and J3 respectively to change. Press SW34 switch (SW27 in power unit 2) to reset the over-temperature protection circuit at the end of the procedure. Make sure that D2 red LED is off (D34 in power unit 2).

Figure 18: Trimmer and test point used to set the threshold for the over-temperature protection circuit. The switch is used to reset the circuit after the occurrence of an over-temperature condition

### 9.2 Setting the current thresholds

Each 1.8V power supply channel is protected by an independent over-current circuit with a default threshold of 1.5A for the digital channels and 250mA for the analog channels. The 16 default current thresholds may be modified via I2C using four on-board 12-bit DAC IC. Each of these DAC IC controls the thresholds for 4 supply channels. Table 18 describes a generic I2C transaction to the "I2C main interface" to set the threshold of a given channel (or group of channels).

Table 18: Single transaction used to set one or all current threshold for the over-current circuits (all values are binary)

| Trans type | Slave address + R/ | W bit | Instruction | Data byte 1         | Data byte 2              |

|------------|--------------------|-------|-------------|---------------------|--------------------------|

| write      | [SL_ADDR]          | 0     | 0011[TH_ID] | $[I_{th}^{DIG}$ _H] | $[I_{th}^{DIG}\_L]$ xxxx |

The 7-bit field SL\_ADDR is the full slave address of one of the DAC IC on the power unit. The 4-bit field TH\_ID represents the identification number of the DAC channel on the selected DAC IC. See Table 19 for details about the possible combinations of SL\_ADDR and TH\_ID.

The 8-bit and 4-bit fields ( $I_{th}^{DIG}$ \_H and  $I_{th}^{DIG}$ \_L) in Table 18 are the most and least significant part of the digital value ( $I_{th}^{DIG}$ ) of the current threshold ( $I_{th}$ ). This value has to be derived from the following formula:

$$I_{th}^{DIG} = 410 + \frac{3685}{3A} I_{th}$$

Table 19: List of the values for SL\_ADDR and TH\_ID field and related functions

| SL_ADDR | TH_ID | Function                                          |

|---------|-------|---------------------------------------------------|

|         | 0000  | Set threshold for Module 1 analog voltage (CH1)   |

|         | 0001  | Set threshold for Module 1 digital voltage (CH2)  |

| 0x52    | 0010  | Set threshold for Module 2 analog voltage (CH3)   |

|         | 0011  | Set threshold for Module 2 digital voltage (CH4)  |

|         | 1111  | Broadcast: set thresholds for CH1-4               |

|         | 0000  | Set threshold for Module 3 analog voltage (CH5)   |

|         | 0001  | Set threshold for Module 3 digital voltage (CH6)  |

| 0x60    | 0010  | Set threshold for Module 4 analog voltage (CH7)   |

|         | 0011  | Set threshold for Module 4 digital voltage (CH8)  |

|         | 1111  | Broadcast: set thresholds for CH5-8               |

|         | 0000  | Set threshold for Module 5 analog voltage (CH9)   |

|         | 0001  | Set threshold for Module 5 digital voltage (CH10) |

| 0x70    | 0010  | Set threshold for Module 6 analog voltage (CH11)  |

|         | 0011  | Set threshold for Module 6 digital voltage (CH12) |

|         | 1111  | Broadcast: set thresholds for CH9-12              |

|         | 0000  | Set threshold for Module 7 analog voltage (CH13)  |

|         | 0001  | Set threshold for Module 7 digital voltage (CH14) |

| 0x72    | 0010  | Set threshold for Module 8 analog voltage (CH15)  |

|         | 0011  | Set threshold for Module 8 digital voltage (CH16) |

|         | 1111  | Broadcast: set thresholds for CH13-16             |

### 9.3 Adjusting the output voltages

As mentioned previously, this system allows the nominally 1.8V output voltages to be adjusted in the range ~1.5-2.7V (it is however important to not exceed 2.5V, such voltages are indeed out of the ADC dynamic range, see section 9.7). The exact range for the voltages varies from channel to channel due to the non-negligible tolerance on the end-to-end resistance of the 8-bit digital potentiometers used to bias the circuit.

This output voltage adjustment feature can be used to compensate for voltage drops across the power and return paths that connect the power system to the modules, and allow them to operate with power within the operational 1.62V-1.98V range. An I2C transaction to the digital potentiometers via the "I2C main interface" is required to set the voltage to each supply channel on a power unit (see Table 20).

Table 20: Single transaction used to adjust the voltage of the regulators (all values are binary)

| Trans type | Slave address + R/ | W bit | Instruction  | Data byte       |

|------------|--------------------|-------|--------------|-----------------|

| write      | [SL_ADDR]          | 0     | 000000[V_ID] | $R_{out}^{DIG}$ |

The 7-bit field SL\_ADDR is the full slave address of one of the DAC IC on the power unit. 2-bit field V\_ID is used to select one of the four 1.8V channels. See Table 21 for details about the possible combinations of SL\_ADDR and TH\_ID.

The 8-bit  $R_{out}^{DIG}$  field is the digital value of the output resistance of the selected digital potentiometer channel. Its value has to be calculated using the following formula (valid in the range 1.49V-2.72):

$$R_{out}^{DIG} = \frac{V_{out}}{0.00486} - 306$$

where  $V_{out}$  is the output voltage of the targeted channel. Due to the tolerance on the end-to-end resistance of the digital potentiometers this formula is affected by 20% error maximum (the on-board ADC channels can be used to calibrate the output voltage settings or other precision methods can be used according to the datasheet of AD5254 digital potentiometer)

| SL_ADDR | V_ID | Function                                         |  |

|---------|------|--------------------------------------------------|--|

|         | 00   | Set threshold for Module 1 analog voltage (CH1)  |  |

| 0x2C    | 01   | Set threshold for Module 1 digital voltage (CH2) |  |

| UXZC    | 10   | Set threshold for Module 2 analog voltage (CH3)  |  |

|         | 11   | Set threshold for Module 2 digital voltage (CH4) |  |

|         | 00   | Set threshold for Module 3 analog voltage (CH5)  |  |

| 0x2D    | 01   | Set threshold for Module 3 digital voltage (CH6) |  |

|         | 10   | Set threshold for Module 4 analog voltage (CH7)  |  |

|      | 11Set threshold for Module 4 digital voltage (C |                                                   |

|------|-------------------------------------------------|---------------------------------------------------|

|      | 00                                              | Set threshold for Module 5 analog voltage (CH9)   |

| 0x2E | 01                                              | Set threshold for Module 5 digital voltage (CH10) |

| UXZE | 10                                              | Set threshold for Module 6 analog voltage (CH11)  |

|      | 11                                              | Set threshold for Module 6 digital voltage (CH12) |

|      | 00                                              | Set threshold for Module 7 analog voltage (CH13)  |

| 0x2F | 01                                              | Set threshold for Module 7 digital voltage (CH14) |

| UXZF | 10                                              | Set threshold for Module 8 analog voltage (CH15)  |

|      | 11                                              | Set threshold for Module 8 digital voltage (CH16) |

Once a digital potentiometer has been set, the selected value can be stored permanently inside the digital potentiometer itself so that it is automatically recalled any time the system is powered on. This can be done performing the transaction described in Table 22.

Table 22: Single transaction used to set the non-volatile memory of a digital potentiometer (all values are binary)

| Trans type | Slave address + R/W bit |   | Instruction  |

|------------|-------------------------|---|--------------|

| write      | [SL_ADDR]               | 0 | 100100[V_ID] |

The values stored in the digital potentiometers can be recalled at any time using the transaction described in Table 23.

Table 23: Single transaction used to recall a value from the non-volatile memory of a digital potentiometer (all values are binary)

| Trans type | Slave address + R/W bit | Instruction |              |

|------------|-------------------------|-------------|--------------|

| write      | [SL_ADDR]               | 0           | 000100[V_ID] |

### 9.4 Setting the bias voltages

Each power unit embeds 8 additional low-current channels that can be used to bias up to 8 sensor modules. These bias circuits include a negative voltage regulator controlled by an 8-bit digital potentiometer - which generates a common voltage for the 8 low-current channels (range from GND to -4.5V) – and 8 FET double switches that provide either a solid connection to ground or to the adjustable voltage coming from the negative voltage regulator. This section describes how to set the output voltage of the regulator performing an I2C transaction to the digital potentiometer via the "I2C main interface" (see Table 24). For details on how to drive the double switches to switch between ground and the negative voltage refer to section 9.5.

Table 24: Single transaction used to set the bias voltage for the substrates of the sensors (all values are binary)

| Trans type | Slave address + R/ | W bit | Instruction | Data byte                        |

|------------|--------------------|-------|-------------|----------------------------------|

| write      | 0101001            | 0     | 00010001    | R <sup>DIG</sup> <sub>bias</sub> |

The 8-bit  $R_{bias}^{DIG}$  field is the digital value of the bias voltage to be applied to the sensors. This value has to be chosen using the following equation

$$V_{bias} = -\frac{5}{125} R_{bias}^{DIG}$$

The bias voltage may saturate around and above  $R_{bias}^{DIG}$  values of 125 depending on the end-to-end resistance of the digital potentiometer (25% tolerance). Once the digital potentiometer has been set, the selected value can be stored permanently inside the digital potentiometer itself so that it is automatically recalled any time the system is powered on. This can be done performing the transaction described in Table 25.

Table 25: Single transaction used to set the non-volatile memory of the digital potentiometer (all values are binary)

| Trans type | Slave address + R/ | W bit | Instruction | Data byte |

|------------|--------------------|-------|-------------|-----------|

| write      | 0101001            | 0     | 01010001    | XXXXXXXX  |

Furthermore the value stored in the digital potentiometer can be recalled at any time according to the procedure at Table 26.

Table 26: Single transaction used to recall the value written in the non-volatile memory of the digital potentiometer

| Tra | ns type | Slave address + R/ | W bit | Instruction | Data byte |

|-----|---------|--------------------|-------|-------------|-----------|

| ١   | write   | 0101001            | 0     | 01100001    | XXXXXXXX  |

### 9.5 ENABLING SUPPLY AND BIAS CHANNELS

Once the current thresholds and all the voltages are set, it is possible to switch on the output channels of the power unit using two on-board open drain IO expanders each driving 8 supply channels. A generic transaction to access these IO expanders via the "I2C aux interface" is shown in Table 27.

Table 27: Single transaction used to activate the supply outputs on a power unit (all values are binary)

| Trans type | Slave address + R/ | Data byte |         |

|------------|--------------------|-----------|---------|

| write      | [SL_ADDR]          | 0         | [IO_EN] |

The 7-bit field SL\_ADDR is the full slave address of one of the two IO expander IC on the power unit. The 8-bit field IO\_EN is used to enable or disable up to 8 supply channels per digital potentiometer IC. See Table 28 for details about the possible combinations of SL\_ADDR and IO\_EN.

| SL_ADDR | IO_EN bits | Description                    |

|---------|------------|--------------------------------|

|         | 0          | Enable Module 1 analog – CH1   |

|         | 1          | Enable Module 1 digital – CH2  |

|         | 2          | Enable Module 2 analog – CH3   |

| 0x38    | 3          | Enable Module 2 digital – CH4  |

| 0,20    | 4          | Enable Module 3 analog – CH5   |

|         | 5          | Enable Module 3 digital – CH6  |

|         | 6          | Enable Module 4 analog – CH7   |

|         | 7          | Enable Module 4 digital – CH8  |

|         | 0          | Enable Module 5 analog – CH9   |

|         | 1          | Enable Module 5 digital – CH10 |

|         | 2          | Enable Module 6 analog – CH11  |

| 0x39    | 3          | Enable Module 6 digital – CH12 |

| 0,55    | 4          | Enable Module 7 analog – CH13  |

|         | 5          | Enable Module 7 digital – CH14 |

|         | 6          | Enable Module 8 analog – CH15  |

|         | 7          | Enable Module 8 digital – CH16 |

Table 28: IO\_EN field bits state and functions for supply voltages IO expanders

In order to enable a 1.8V channel, the corresponding bit has will be set high. The red LED that signals an overcurrent condition (on at board power on) will switch off and the channel green LED will switch on (since its brightness depends on the output voltage of the channel it may not be visible). The channel will stay enabled until an overcurrent condition occurs. However it can be switched off following one of the two procedures:

- Triggering the over-current protection circuit. The current threshold for the channel is lowered below the current drawn by the channel (can be set to 0x000). This will trigger the over-current protection circuit (the green LED will be switched off and the red LED will be switched back on).

- Disabling the regulator. The corresponding bit in the IO\_EN string is lowered. The green LED will be switched off but the red LED will not be switched on (no overcurrent condition has occurred).

As already mentioned, each of the bias outputs can be either grounded or tied to a specific negative voltage level adjustable in the range from GND to -4.5V. In order to switch between the two voltage levels it is necessary to perform a write transaction to an IO expander via the "I2C main interface" as shown in Table 29.

#### Table 29: Single transaction used to activate the supply outputs on a power unit (all values are binary)

| Trans ty | pe | Slave address + R/ | Data byte |         |

|----------|----|--------------------|-----------|---------|

| write    |    | 0111000            | 0         | [IO_EN] |

The 8-bit field IO\_EN must be set according to Table 30 to either ground the bias channels or set them to a negative voltage.

### Table 30: IO\_EN field bits state and functions for bias IO expander

| SL_ADDR | IO_EN bits | State                      |                                          |  |

|---------|------------|----------------------------|------------------------------------------|--|

|         |            | high (default @ poweron)   | low                                      |  |

|         | 0          | Bias channel 1 is grounded | Bias channel 1 set to adjustable voltage |  |

|         | 1          | Bias channel 2 is grounded | Bias channel 2 set to adjustable voltage |  |

|         | 2          | Bias channel 3 is grounded | Bias channel 3 set to adjustable voltage |  |

| 0x38    | 3          | Bias channel 4 is grounded | Bias channel 4 set to adjustable voltage |  |

| UX50    | 4          | Bias channel 5 is grounded | Bias channel 5 set to adjustable voltage |  |

|         | 5          | Bias channel 6 is grounded | Bias channel 6 set to adjustable voltage |  |

|         | 6          | Bias channel 7 is grounded | Bias channel 7 set to adjustable voltage |  |

|         | 7          | Bias channel 8 is grounded | Bias channel 8 set to adjustable voltage |  |

It has to be noticed that there is no LED that indicates whether the bias voltage is at a voltage lower than ground.

The system allows one to monitor the voltage at the output of the negative voltage regulator and the total current drawn by all the FET switches (refer to section 9.7 for more details on this monitoring feature).

### 9.6 CHECKING REMOTELY THE STATUS OF THE POWER OUTPUTS

During operation of the power system one of the following events may occur:

- The system is automatically switched off due to an over-temperature condition. D2 LED (D34 LED in the case of power unit 2) will turn on and the downstream circuitry, which includes the 16 1.8V channels (but not the bias circuit) will be switched off together with any other LEDs.

- 2) One or more 1.8V channels are switched off due to the occurrence of over-current conditions. In such case the green LEDs that correspond to the channels where the over-current conditions occurred will be switched off and the corresponding red LEDs will be switched on.

Either condition can be remotely identified by performing read transactions to the IO expanders previously used to enable the power/bias channels. Perform a read transaction to the IO expanders

as shown in Table 31 via the "I2C main interface" for reading the status of the bias channels and via the "I2C aux interface" for reading the status of the supply channels.

Table 31: Read transaction to the on-board IO module (grey for bytes transferred from master to slave, white for bytes transferred from slave to master)

| Trans type | Slave address + R | Data byte |           |

|------------|-------------------|-----------|-----------|

| read       | [SL_ADDR]         | 1         | [IO_STAT] |

The 8-bit IO\_STAT field contains the status of the power/bias channels (see Table 32). Since it is unlikely that an over-current condition occurs simultaneously in 16 power channels, if all the 16 power channels are found to be disabled, this may be due to an over-temperature condition.

Table 32: IO\_STAT field bits state and functions for supply/bias voltages IO expanders

|           |              | Sta                              | atus                            |

|-----------|--------------|----------------------------------|---------------------------------|

| SL_ADDR   | IO_STAT bits | Low                              | High                            |

|           | 0            | Module 1 analog – CH1 disabled   | Module 1 analog – CH1 enabled   |

|           | 1            | Module 1 digital – CH2 disabled  | Module 1 digital – CH2 enabled  |

| 0x38      | 2            | Module 2 analog – CH3 disabled   | Module 2 analog – CH3 enabled   |

| (I2C aux  | 3            | Module 2 digital – CH4 disabled  | Module 2 digital – CH4 enabled  |

| channel)  | 4            | Module 3 analog – CH5 disabled   | Module 3 analog – CH5 enabled   |

| channely  | 5            | Module 3 digital – CH6 disabled  | Module 3 digital – CH6 enabled  |

|           | 6            | Module 4 analog – CH7 disabled   | Module 4 analog – CH7 enabled   |

|           | 7            | Module 4 digital – CH8 disabled  | Module 4 digital – CH8 enabled  |

|           | 0            | Module 5 analog – CH9 disabled   | Module 5 analog – CH9 enabled   |

|           | 1            | Module 5 digital – CH10 disabled | Module 5 digital – CH10 enabled |

| 0x39      | 2            | Module 6 analog – CH11 disabled  | Module 6 analog – CH11 enabled  |

| (I2C aux  | 3            | Module 6 digital – CH12 disabled | Module 6 digital – CH12 enabled |

| channel)  | 4            | Module 7 analog – CH13 disabled  | Module 7 analog – CH13 enabled  |

| channely  | 5            | Module 7 digital – CH14 disabled | Module 7 digital – CH14 enabled |

|           | 6            | Module 8 analog – CH15 disabled  | Module 8 analog – CH15 enabled  |

|           | 7            | Module 8 digital – CH16 disabled | Module 8 digital – CH16 enabled |

|           | 0            | Module 1 bias – CH1 adj voltage  | Module 1 bias – CH1 grounded    |

|           | 1            | Module 2 bias – CH2 adj voltage  | Module 2 bias – CH2 grounded    |

| 0x38      | 2            | Module 3 bias – CH3 adj voltage  | Module 3 bias – CH3 grounded    |

| (I2C main | 3            | Module 4 bias – CH4 adj voltage  | Module 4 bias – CH4 grounded    |

| channel)  | 4            | Module 5 bias – CH5 adj voltage  | Module 5 bias – CH5 grounded    |

| channely  | 5            | Module 6 bias – CH6 adj voltage  | Module 6 bias – CH6 grounded    |

|           | 6            | Module 7 bias – CH7 adj voltage  | Module 7 bias – CH7 grounded    |

|           | 7            | Module 8 bias – CH8 adj voltage  | Module 8 bias – CH8 grounded    |

### 9.7 MONITORING THE OUTPUT VOLTAGES AND CURRENTS

An important functionality of each power unit is the possibility to monitor all the generated power/bias voltages and the corresponding currents using a total of 5 8-channel ADC IC. This feature can be used during operation both to check the overall status of the system, e.g. protection status and/or spot malfunctioning, and as feedback mechanism to finely adjust the output voltages of the power supply channels.